## bookboon.com

## CMOS Integrated Circuit Simulation with LTspice IV

a Tutorial Guide Erik Bruun

Download free books at

bookboon.com

Erik Bruun

# CMOS Integrated Circuit Simulation with LTspice IV – a Tutorial Guide

CMOS Integrated Circuit Simulation with LTspice IV – a Tutorial Guide 1st edition

© 2015 Erik Bruun & <u>bookboon.com</u>

ISBN 978-87-403-1059-7

Peer reviewed by Dennis Øland Larsen, IC design engineer, GN ReSound

## Contents

| Preface                                                                           | 7  |

|-----------------------------------------------------------------------------------|----|

| Getting started                                                                   | 9  |

| Tutorial 1 – Resistive Circuits                                                   | 13 |

| Example 1.1: A resistor circuit                                                   | 13 |

| Example 1.2: A transconductance amplifier                                         | 27 |

| Example 1.3: A current amplifier.                                                 | 32 |

| Problems                                                                          | 38 |

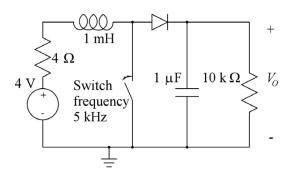

| Tutorial 2 – Circuits with Capacitors and Inductors                               | 43 |

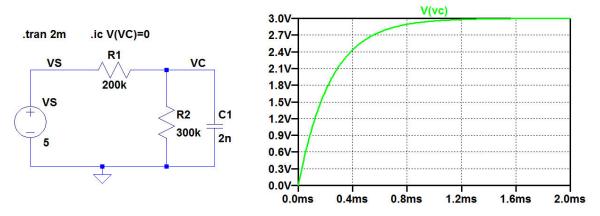

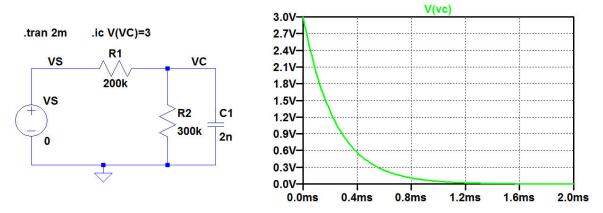

| Example 2.1: An RC network                                                        | 43 |

| Example 2.2: A half-wave rectifier with a smoothing filter                        | 50 |

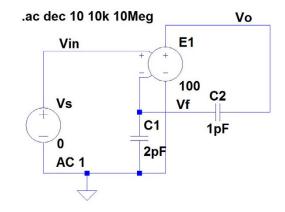

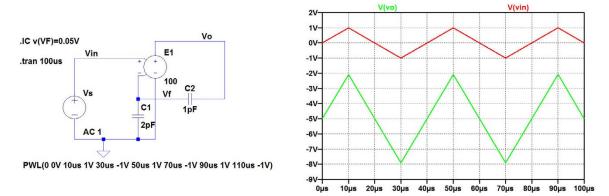

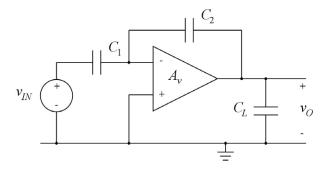

| Example 2.3: An amplifier with capacitive feedback network                        | 52 |

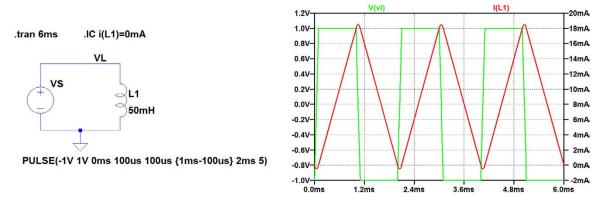

| Example 2.4: An ideal inductor.                                                   | 55 |

| Example 2.5: Revisiting the capacitor charging and discharging                    | 57 |

| Problems                                                                          | 63 |

| Tutorial 3 – MOS transistors                                                      | 67 |

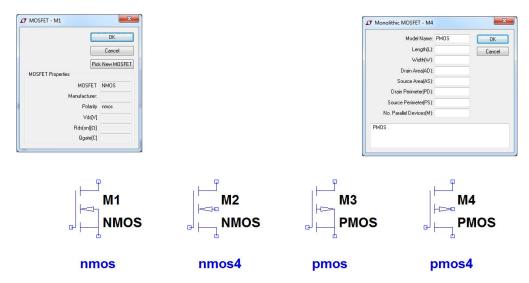

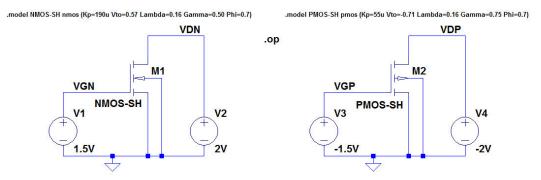

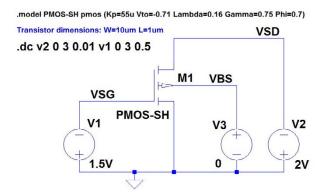

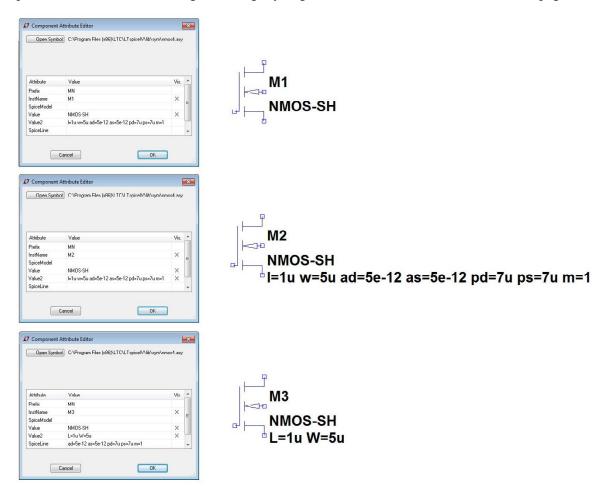

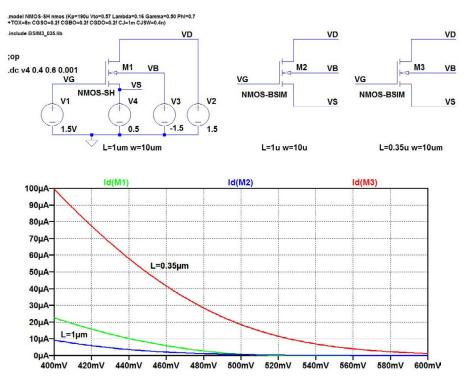

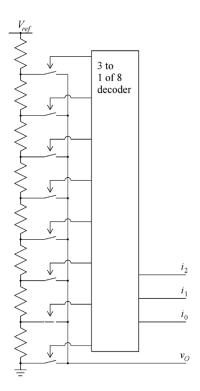

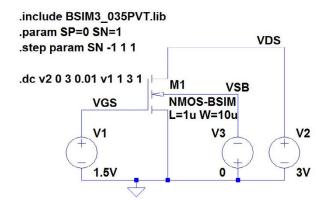

| Example 3.1: Different MOS transistor symbols and models in LTspice               | 67 |

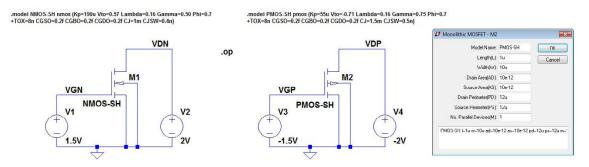

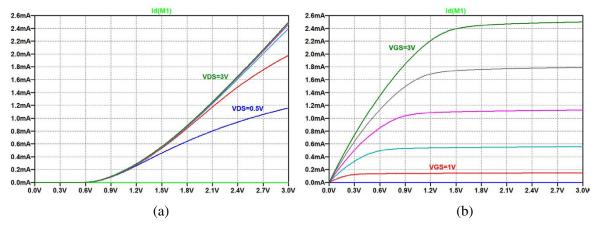

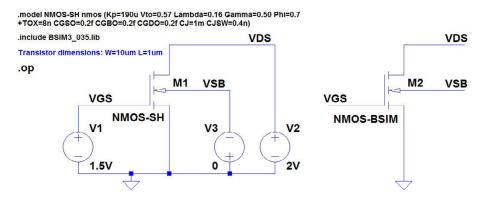

| Example 3.2: Advanced transistor models                                           | 75 |

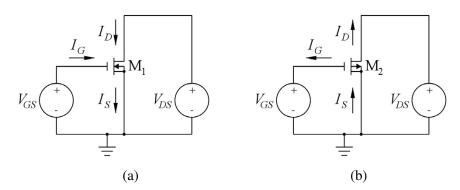

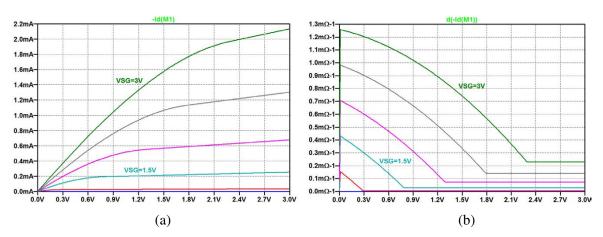

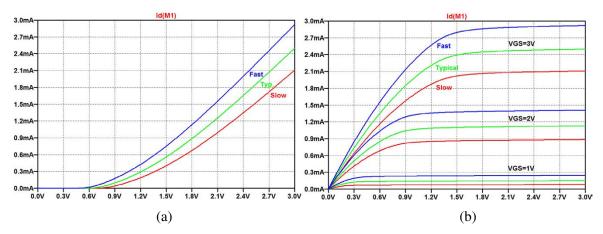

| Example 3.3: MOS transistor input characteristics                                 | 79 |

| Example 3.4: MOS transistor output characteristics                                | 84 |

| Example 3.5: Deriving transistor parameters from input and output characteristics | 86 |

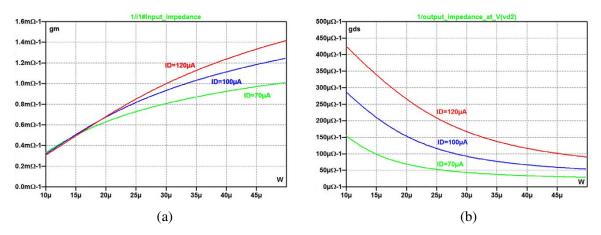

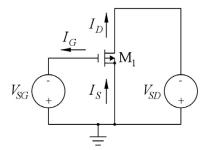

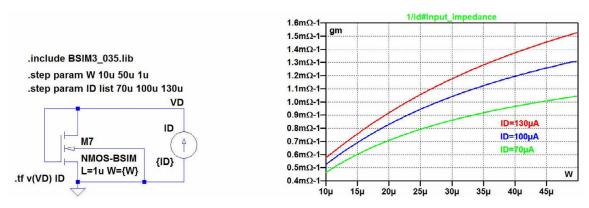

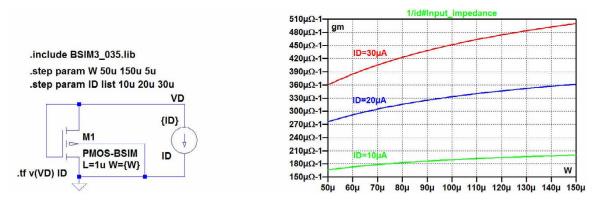

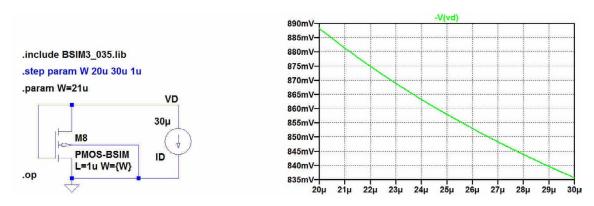

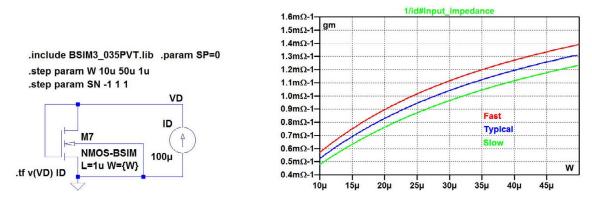

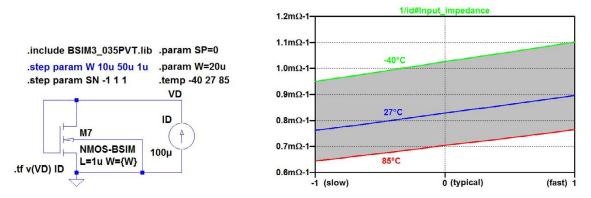

| Example 3.6: Simulating small signal parameters using the '.tf' simulation        | 90 |

| Problems                                                                          | 98 |

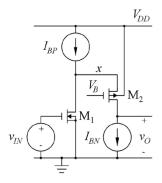

| Tutorial 4 – Basic gain stages                                                 | 103 |

|--------------------------------------------------------------------------------|-----|

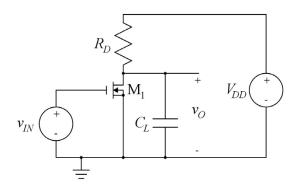

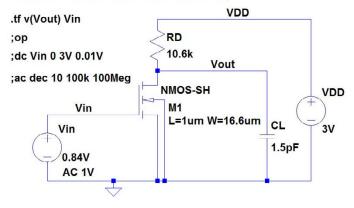

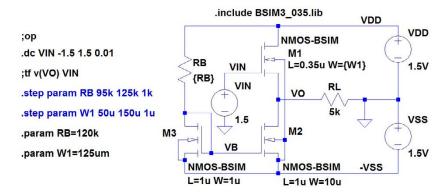

| Example 4.1: The common source amplifier (inverting amplifier)                 | 103 |

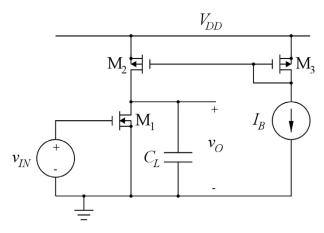

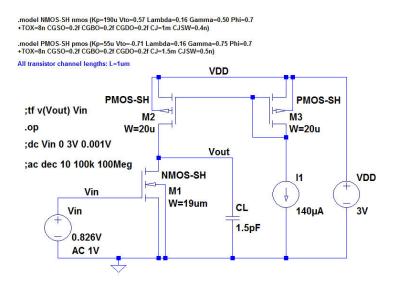

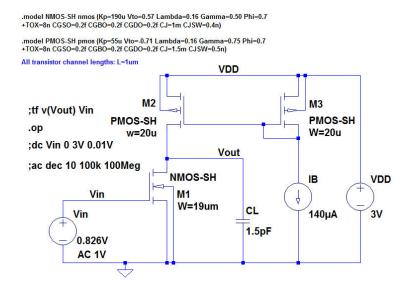

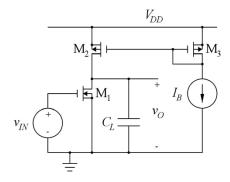

| Example 4.2: The common drain amplifier (source follower)                      | 114 |

| Example 4.3: The common gate amplifier                                         | 121 |

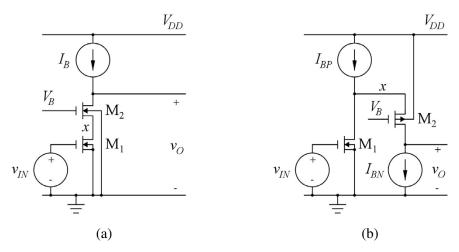

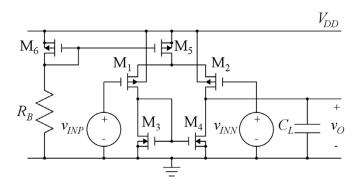

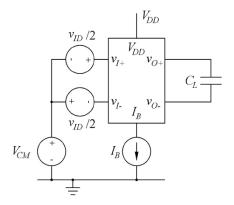

| Example 4.4: The differential pair                                             | 126 |

| Problems                                                                       | 140 |

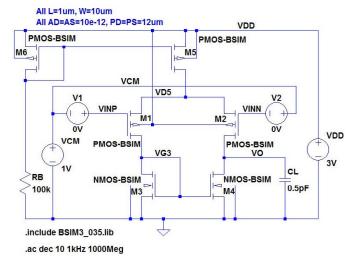

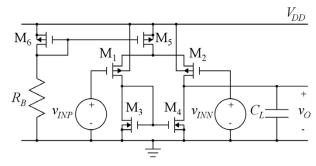

| Tutorial 5 – Hierarchical design                                               | 147 |

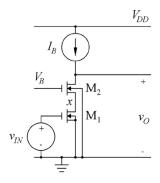

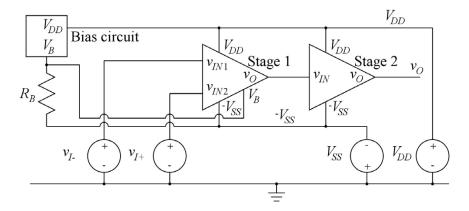

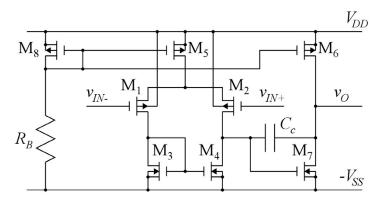

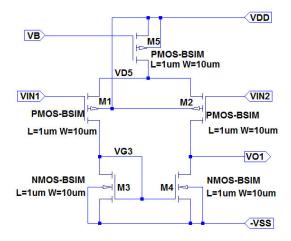

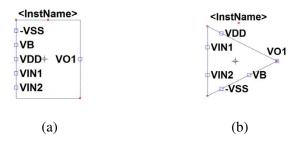

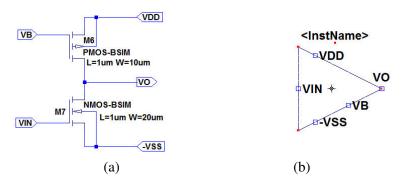

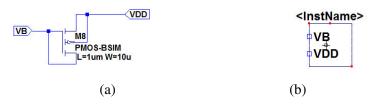

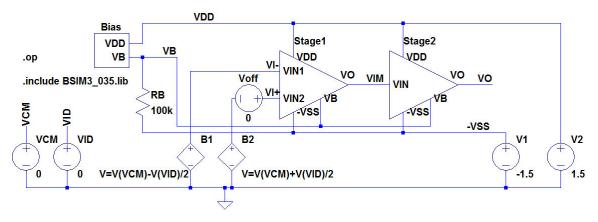

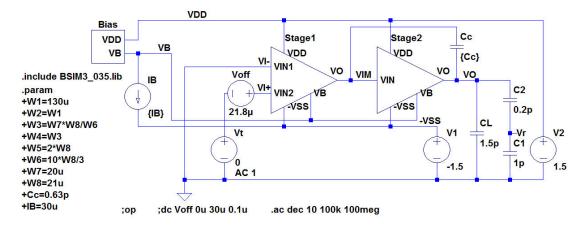

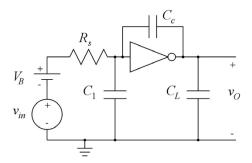

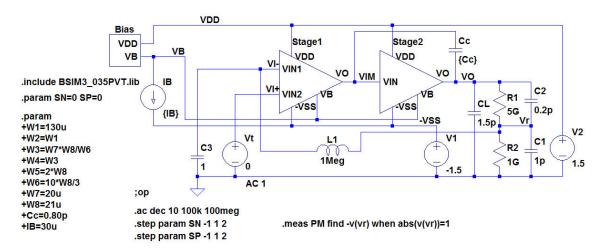

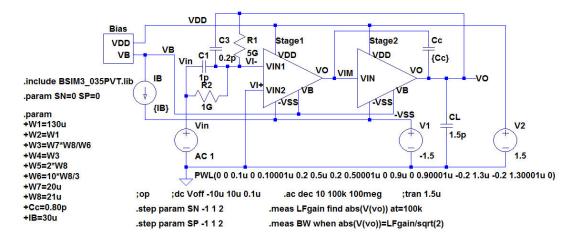

| Example 5.1: A two stage operational amplifier                                 | 147 |

| Example 5.2: Designing the two stage opamp for an inverting feedback amplifier | 154 |

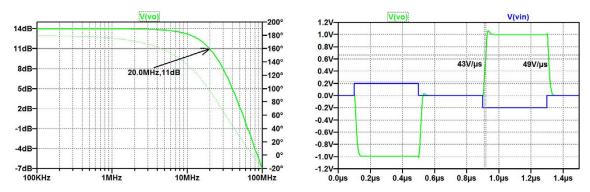

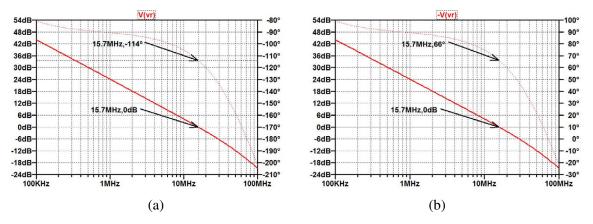

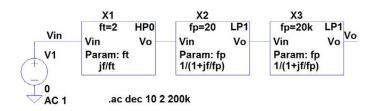

| Example 5.3: Generic filter blocks                                             | 165 |

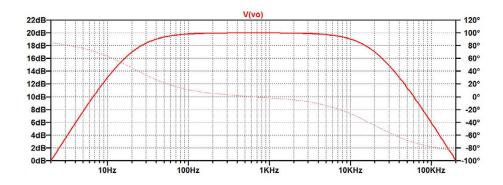

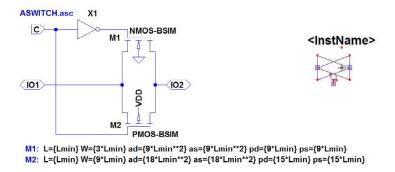

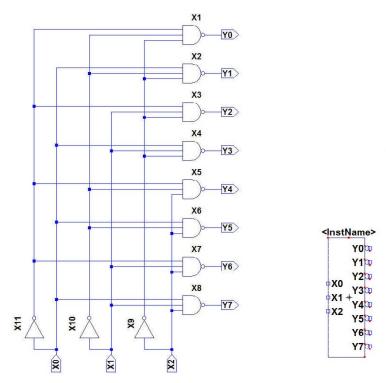

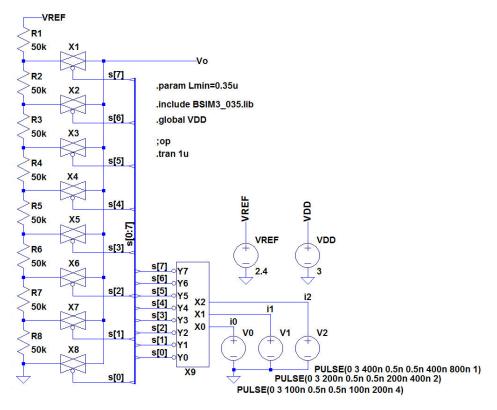

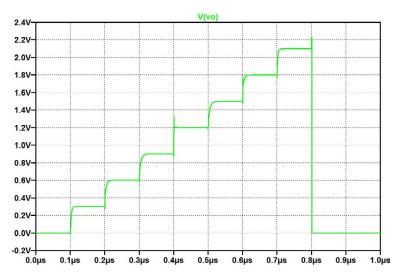

| Example 5.4: A mixed analog/digital circuit                                    | 168 |

| Problems                                                                       | 175 |

| Tutorial 6 – Process and parameter variations                                  | 179 |

| Example 6.1: Model files for corner simulations                                | 180 |

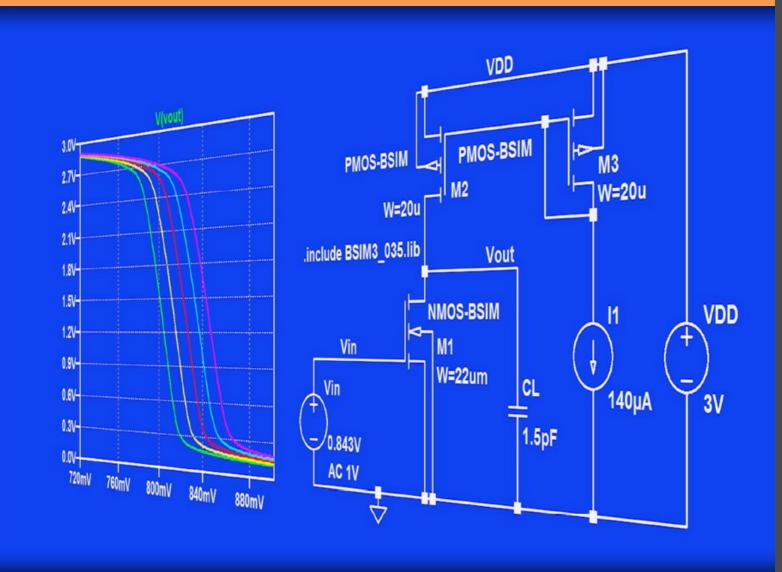

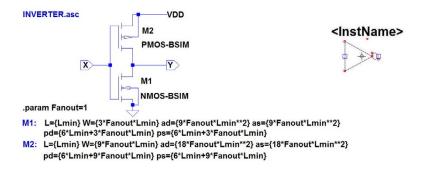

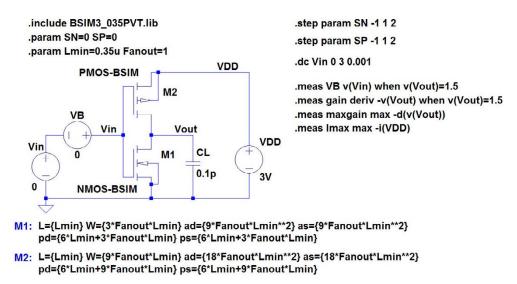

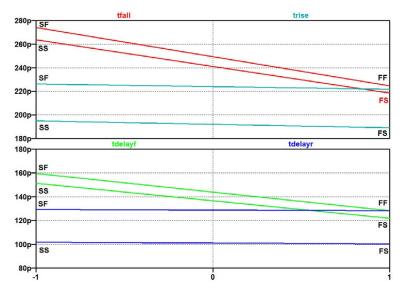

| Example 6.2: An inverter                                                       | 187 |

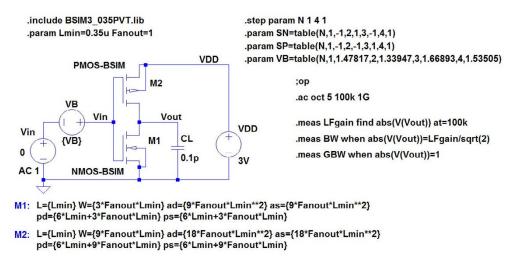

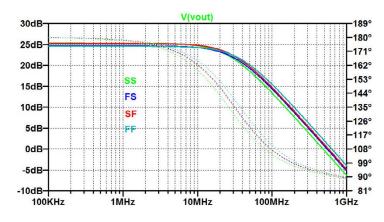

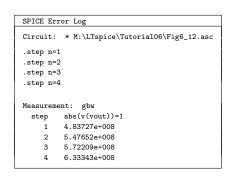

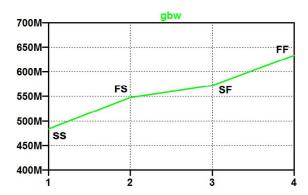

| Example 6.3: A test bench for the two stage opamp                              | 196 |

| Example 6.4: Monte Carlo simulation                                            | 198 |

| Problems                                                                       | 206 |

| Tutorial 7 – Importing and exporting files                          | 211 |

|---------------------------------------------------------------------|-----|

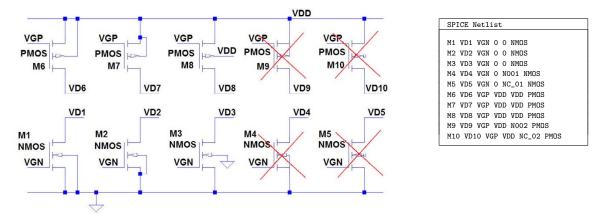

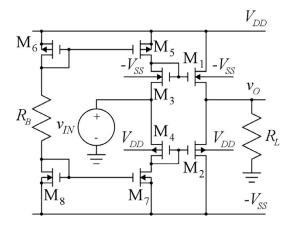

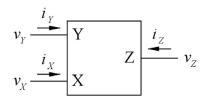

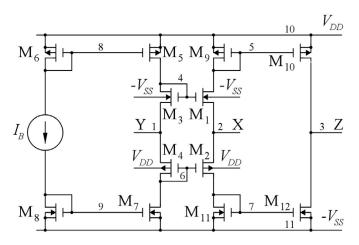

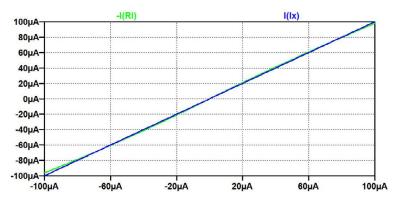

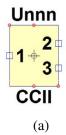

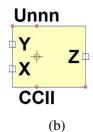

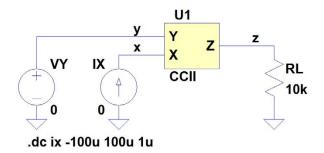

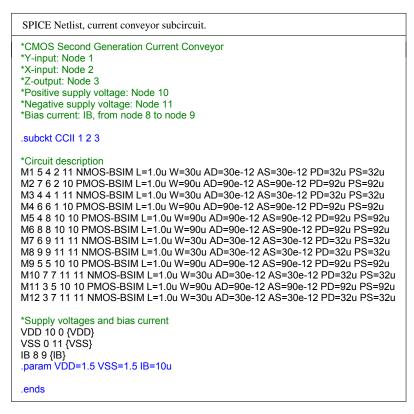

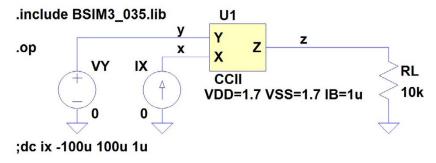

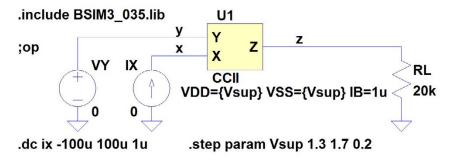

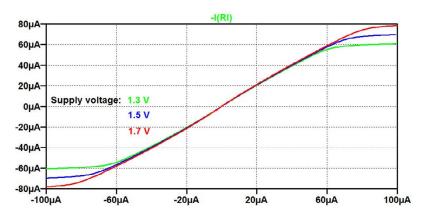

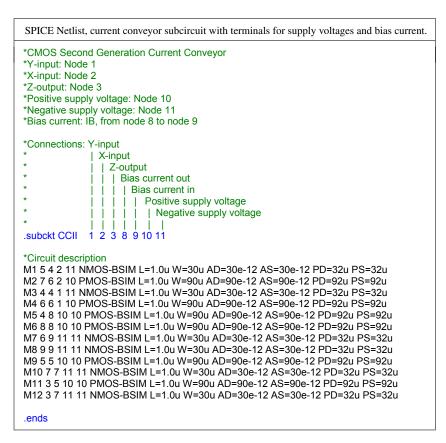

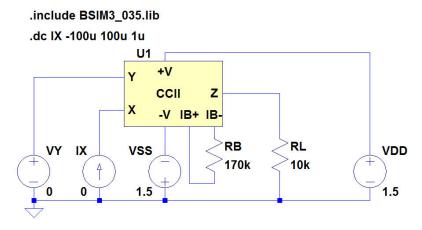

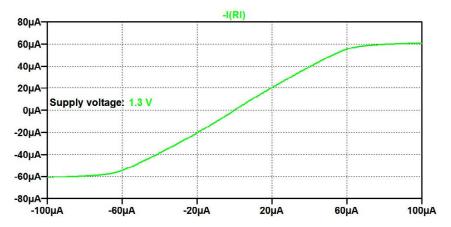

| Example 7.1: Importing a netlist file describing a current conveyor | 211 |

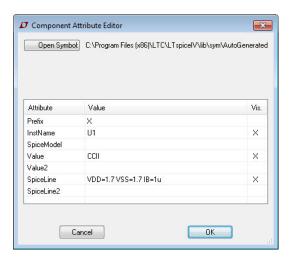

| Example 7.2: Creating a subcircuit from a netlist                   | 215 |

| Example 7.3: Exporting a netlist                                    | 221 |

| Example 7.4: Exporting other files                                  | 223 |

| Problems                                                            | 227 |

| Moving on                                                           | 231 |

| Appendix A –                                                        |     |

| A beginner's guide to components and simulation commands in LTspice | 233 |

| Appendix B –                                                        |     |

| BSIM transistor models for use in LTspice                           | 241 |

| Index                                                               | 245 |

Discover the truth at www.deloitte.ca/careers

### **Preface**

This book is about circuit simulation with the simulation program LTspice. It is intended as an introduction to LTspice and to simulation of CMOS integrated circuits with LTspice. It may serve as a supplementary textbook for an introductory course in analog integrated circuit design. The first tutorials can also be used as a general introduction to circuit simulation in an introductory course in electronic circuits. The book can be used for classroom teaching, and it can also be used for self-study. It is based on LTspice for Windows.

Tutorials 1 and 2 introduce the fundamental concept of the circuit simulator demonstrated on circuits using passive devices (resistors, capacitors and inductors) and ideal voltage sources and current sources, both independent sources and controlled sources.

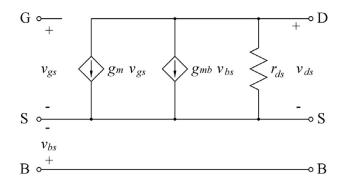

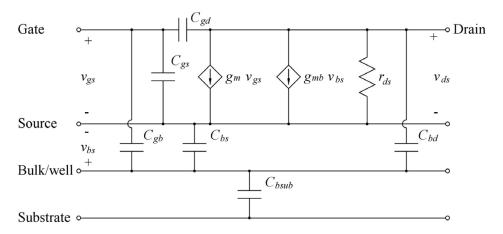

Tutorial 3 is about MOS transistor models and gives an introduction to the standard Shichman-Hodges transistor model often used for hand calculations when analyzing CMOS circuits. Also, it provides an introduction to more advanced transistor models and a comparison between the advanced transistor models and the simple Shichman-Hodges model.

Tutorial 4 gives examples of basic CMOS amplifier stages, i.e. common source, common drain, common gate and differential pair. Both analysis and design approaches using LTspice are shown.

Tutorial 5 shows how the basic stages can be defined as subcircuits and combined into a multistage operational amplifier. Also given in this tutorial is a design example of a two stage opamp for a feedback amplifier, generic filter blocks and a mixed analog/digital circuit. The tutorial is an introduction to hierarchical design.

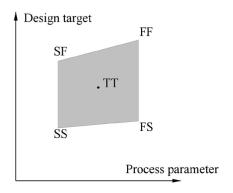

Tutorial 6 is about the simulation of process and parameter variations in a circuit. In integrated circuit design, process variations pose a major challenge to the designer. Often technology files are supplied for typical process parameters and a selection of worst case process parameters. The tutorial gives an introduction to simulation with technology files including process variations. Also supply voltage variations and temperature variations are considered. Together, these variations are termed PVT variations.

Tutorial 7 is about import of netlist files and export of output files from LTspice. The netlist files are the primary descriptive files for a circuit to be simulated by Spice. There are minor differences between netlist files originating from LTspice and other versions of Spice, but in general it is rather straightforward to modify a netlist file to be compatible with LTspice. Several textbooks provide examples of netlist files which may be used for simulation with LTspice. A schematic is not needed. The simulation commands in LTspice can be executed directly from the netlist files.

End-of-chapter problems are provided for all tutorials to further illustrate the subject of the tutorials.

Finally, two appendices are included. Appendix A is a beginner's guide which may facilitate quick and easy learning of LTspice for the reader or student who is new to LTspice. Appendix B provides a number of BSIM transistor model files for use in LTspice. The files may be copied directly from the electronic version of this book into a text editor.

**Acknowledgements:** The author would like to acknowledge the many students who have contributed with comments and suggestion for the book. Also, a particular acknowledgement goes to my colleague Dennis Øland Larsen who reviewed the entire manuscript and provided many useful comments and corrections during the final phase of writing.

## Getting started

The program LTspice is freely available from Linear Technology,

http://www.linear.com/designtools/software/.

Just click 'Download LTspice' and follow the instructions. You may register for an account with Linear Technology, but you do not have to. You may just click 'No thanks, just download the software' and choose 'Run' in the dialogue box which appears.

A 'Getting started guide' is available from

http://cds.linear.com/docs/en/software-and-simulation/LTspiceGettingStartedGuide.pdf.

This book is addressing the simulation of integrated circuits, in particular CMOS circuits, so we will not go into detail with the simulation of circuits with standard components but refer the reader to the many examples of demo circuits using standard components which are found on the LTspice website. Here you will also find a blog with several hints and video clips on how to use LTspice.

In addition, comprehensive books and guides about Spice can be found, (Tuinenga 1995) and (Vladimirescu 1994), and a manual dedicated to LTspice is also available (Brocard 2013). However, the program is fairly easy and intuitive and once the installation is complete, you may go directly to the first tutorial, providing you with examples of circuits using resistors, voltage sources and current sources. A 'learning by doing' approach is perfectly feasible with LTspice. The program also includes a 'help' function with detailed descriptions of the commands and options in the program. The keyboard shortcut to 'help' is 'F1' in the windows version and '\mathbb{R}?' in the Mac version. If you want a paper manual for the program, you can get it using the 'help' function: Just open 'help', click on the 'Print' symbol and select 'Print the selected heading and all subtopics' in the dialogue box which opens. Your printer should be ready for printing about 130 pages.

This book is based on the Windows version of LTspice. The program is also available for Mac. There are some differences in the user interface of the two versions. This might be somewhat confusing for first-time users. As a guide to Mac users, the following page provides a list of some of the differences which may initially cause confusion.

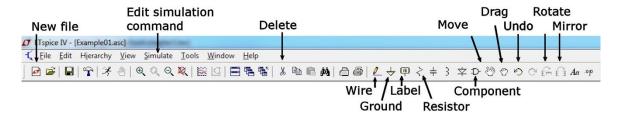

- The toolbar shown in fig. 1.2 on page 14 is not available in the Mac version. Instead, a right click on the drawing sheet will open a menu with several sub-menus. The 'Draft' sub-menu allows you to insert 'Components', 'Wires', 'Net Names', 'SPICE Directives', etc. In particular, you should notice that the ground symbol is not available via 'Components', but it can be inserted using the keyboard shortcut (hotkey) 'G' or using 'Net Names' as explained on page 15.

- The editing commands ('Move', 'Drag', 'Duplicate', etc.) are found in the 'Edit' submenu. The rotate and mirror operations are available via '\R' and '\R'.

- The 'Simulate' command shown in fig. 1.2 on page 14 and described on page 16 is not available in the Mac version. Instead, use 'SPICE Directives' from the 'Draft' sub-menu and type in the appropriate simulation command. The help function provided by the window shown in fig. 1.5 on page 18 with different tabs for the different simulation commands can be opened by right clicking in the 'SPICE Directives' dialogue box. This opens a 'Help me edit' option where you can select 'Analysis Cmd'. A similar help function is available for '.step' commands.

- The result of a 'DC operating point' simulation ('.op') is not automatically displayed in a window like shown in fig. 1.6 on page 18. Instead, a plot window opens, and you can select the currents and voltages to be displayed by pointing to relevant components and nodes in the schematic as described on page 23. If you want the simulation result in a format as shown in fig. 1.6, open the 'Spice Error Log' from the 'View' sub-menu or by '光L'.

- The results of a 'DC Transfer' simulation ('.tf') are not displayed in a window like shown in fig. 1.21 on page 32. Instead, a plot window opens, and using 'Add Traces' from the plot window, you can select the transfer function, the input resistance and the output resistance.

- When selecting a new 'Simulate' command, previous simulation commands are not automatically changed into comments as described on page 23. It must be done manually.

- For transistors, the small signal parameters calculated by a 'DC operating point' simulation

('.op') are listed in the 'Spice Error Log' together with the bias values of voltages and

currents. Also for an 'AC Analysis', the small signal transistor parameters for the bias

point are listed in the 'Spice Error Log'.

- Not only in the schematics sheet but also in waveform plots, a right click opens a menu with several sub-menus.

- The commands for copying schematics and waveform plot to the clipboard are found in the submenu 'View  $\rightarrow$  Paste Bitmap'.

ŠKODA

#### References

SIMPLY CLEVER

Brocard, G. 2013, *The LTspice IV Simulator – Manual, Methods and Applications*, First Edition, Swiridoff Verlag, Künzelsau, Germany.

Tuinenga, PW. 1995, *Spice: A Guide to Circuit Simulation and Analysis Using PSpice*, Third Edition, Prentice Hall, Upper Saddle River, USA.

Vladimirescu, A. 1994, *The SPICE book*, First Edition, John Wiley & Sons, Hoboken, USA.

We will turn your CV into an opportunity of a lifetime

Do you like cars? Would you like to be a part of a successful brand? We will appreciate and reward both your enthusiasm and talent. Send us your CV. You will be surprised where it can take you.

Send us your CV on www.employerforlife.com

### Tutorial 1 - Resistive Circuits

This tutorial is an introduction to the basics of LTspice simulation of resistive circuits with voltage sources and current sources. After having completed the tutorial, you should be able to

- draw circuits using the schematic editor in LTspice.

- specify resistors, independent sources and controlled sources in LTspice.

- recognize the basic netlist structure for simple circuits in LTspice.

- run simulations of operating points, dc sweeps and small signal transfer functions.

- run simulations with parameter sweeps.

- plot simulation results using the waveform viewer of LTspice.

#### Example 1.1: A resistor circuit.

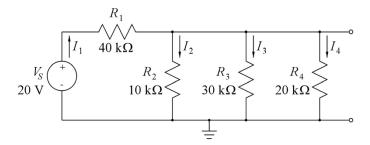

The first example is a simple circuit with four resistors and a voltage source as shown in fig. 1.1:

Figure 1.1: Circuit for first simulation.

**Drawing the circuit:** Start by opening a new file in LTspice ('File  $\rightarrow$  New Schematic' or the leftmost symbol  $\bowtie$  in the Editor toolbar). Next, you should draw the schematic shown in fig. 1.1.

Figure 1.2: Some toolbar symbols.

Click (left mouse click) on the resistor symbol shown in the toolbar (symbol ₹) and place the four resistors. You may rotate a resistor by clicking on the 'rotate' symbol ← on the toolbar or by typing 'Ctrl-R' when placing the resistor. Right click on the mouse (or type 'Esc') to leave the insertion command. As an alternative to picking the resistor from the toolbar, you may use the command 'Edit → Resistor', or you may simply type 'R'. The resistors may now be edited to the correct values and numbers shown in fig. 1.1. Move the cursor to the resistor number (the reference designator, e.g. R1). On the status bar at the bottom of the LTspice program window, a message will appear, telling you that with a right click you can edit the name of the resistor. The right click opens a dialogue box where you can enter the new reference designator. Likewise, the value of the resistor is edited by right clicking R.

A figure pointing out some of the toolbar symbols is shown in fig. 1.2.

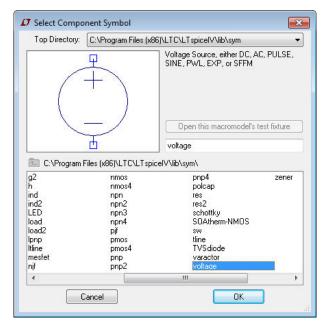

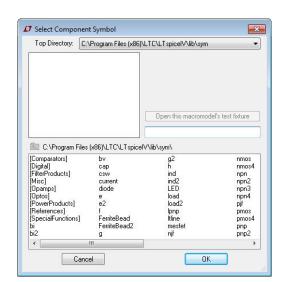

The voltage source  $V_S$  is inserted by selecting the 'Component' symbol on the toolbar, symbol  $\mathfrak{D}$ . Click on the symbol (left click) and a selection box will appear with a large selection of components, see fig. 1.3. Select 'voltage'. This results in the symbol for a voltage source. The value and the designation is edited in the same way as for the resistors. Also for the voltage source, you may use the 'Edit' command instead of picking the symbol from the toolbar ('Edit  $\rightarrow$  Component'), or you may simply type 'F2' which will bring you to the component selection box.

Figure 1.3: Component selection box.

The components are connected together by wires inserted with the 'wire'-symbol (symbol 2) or the keyboard shortcut (hotkey) 'F3'.

Also remember to insert a ground symbol (symbol  $\Rightarrow$  or keyboard shortcut (hotkey) 'G') to indicate the reference voltage of 0 V. If the ground is missing in the schematic, LTspice will not execute a simulation.

It is a good idea to give names to important nodes in the circuit, e.g.  $V_1$  and  $V_2$ , using the symbol 'Label Net' from the toolbar or the hotkey 'F4'. Alternatively, point to a node and right click. This opens a dialogue box where you can select 'Label Net' and type in a name. You can also insert the ground symbol in this way by ticking 'GND(global node 0)' in the dialogue box for 'Net Name'.

If you wish to make adjustments to your schematic, you can move or drag symbols using the hotkeys 'F7' or 'F8', respectively (or symbols 9 and 9 on the toolbar, or the 'Edit  $\rightarrow$  Move' and 'Edit

- → Drag' commands). Also, you can delete a symbol or wire using 'F5', toolbar symbol 🐰 or 'Edit

- $\rightarrow$  Delete', and you can duplicate symbols using 'F6', toolbar symbol  $\rightleftharpoons$  or 'Edit  $\rightarrow$  Duplicate'. These commands work not only on single symbols. When you have activated one of the commands, you can define a box by clicking and dragging using the left mouse button, and the command will work on the entire contents of the box.

The assignment of hotkeys can be seen (and edited) using the command 'Tools  $\rightarrow$  Control Panel  $\rightarrow$  Drafting Options  $\rightarrow$  Hotkeys'.

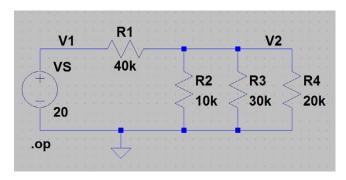

The resulting schematic may look like the schematic shown in fig. 1.4. When the schematic is completed, you should save it (using 'File  $\rightarrow$  Save as') in an appropriate folder for your circuits and using a suitable file name. You can also export the schematic to other programs. A very simple method is to use the command 'Tools  $\rightarrow$  Copy bitmap to Clipboard' and then paste the schematic into another program (e.g. Microsoft Word) from the clipboard (using 'Ctrl-V').

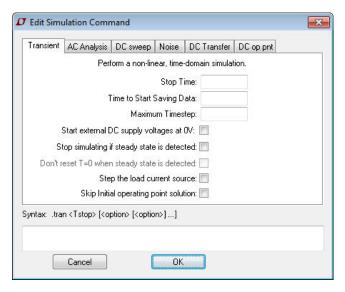

**Simulating the circuit:** Now the circuit is ready to be simulated. For this, we need a simulation command. When selecting the command 'Simulate  $\rightarrow$  Edit Simulation Cmd', a window opens with a number of tabs as shown in fig. 1.5 on page 18. Each tab provides help for the basic simulation modes in LTspice. These are:

- *Transient:* Perform a non-linear time domain simulation. This is used for finding voltages and currents as function of time, e.g. charging and discharging of a capacitor.

- AC Analysis: Compute the small signal AC behavior of the circuit linearized about its DC operating point. This is used for finding the frequency response of a circuit, e.g. the Bode plot of a gain function.

- *DC sweep:* Compute the DC operating point of a circuit while stepping independent sources and treating capacitances as open circuits and inductances as short circuits. This is used for finding voltages and currents as function of one (or more) signals varying in magnitude, e.g. the output voltage of an amplifier as a funtion of the input voltage.

- *Noise:* Perform a stochastic noise analysis of the circuit linearized about its DC operating point. This is used for analyzing the noise performance of a circuit, e.g. finding thermal noise and flicker noise in a gain stage with MOS transistors.

- *DC Transfer:* Find the DC small signal transfer function. This is used for finding small signal input resistance, output resistance and transfer function for a circuit at DC, i.e. the frequency of the input signal source is 0.

- *DC op pnt:* Compute the DC operating point treating capacitances as open circuits and inductances as short circuits. This is used for finding DC voltages and currents in a bias point for a circuit. It is also used for finding small signal parameters of transistors in the bias point.

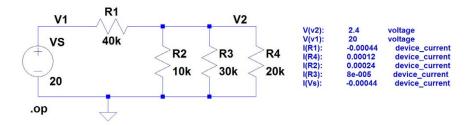

For the first simulation of the circuit in fig. 1.4, we just need to find some DC voltages and currents in some devices. This is done using the simulation command 'DC operating point' (DC op pnt). You open the tab 'DC op pnt' and select the command '.op' by clicking 'OK'. This opens a command line which can now be placed on the schematic by the cursor. Insert the command by a left mouse click or by hitting 'Return'.

Figure 1.4: Schematic from LTspice.

Figure 1.5: Help window for editing the simulation commands.

| Output from DC op pnt simulation |          |                |  |  |

|----------------------------------|----------|----------------|--|--|

| Operating Point                  |          |                |  |  |

| V(v2):                           | 2.4      | voltage        |  |  |

| V(v1):                           | 20       | voltage        |  |  |

| I(R1):                           | -0.00044 | device_current |  |  |

| I(R4):                           | 0.00012  | device_current |  |  |

| I(R2):                           | 0.00024  | device_current |  |  |

| I(R3):                           | 8e-005   | device_current |  |  |

| I(Vs):                           | -0.00044 | device_current |  |  |

Figure 1.6: Simulation result for circuit example from fig. 1.4.

Next, the simulation is run by the command 'Simulate  $\rightarrow$  Run' or by using the 'Run'-symbol  $\mathscr{F}$  on the toolbar. If there are no errors in the schematic, the simulation results in a new window being opened with a list of all node voltages and device currents, see fig. 1.6.

Once you have closed the window, you can re-open it by the command 'View  $\rightarrow$  Visible Traces', toolbar symbol  $\stackrel{\text{\tiny LE}}{\bowtie}$ .

Notice that LTspice inherently specifies a direction of current flow for each of the components. For the voltage source 'VS', the positive direction of current flow is into the positive terminal of the voltage source. In our case, the current is flowing out of the positive terminal of the voltage source, so in fig. 1.6 the current 'I(Vs)' appears with a negative value. Also the current flow in a resistor is defined with a sign. Unfortunately, you cannot from the symbol see which end of the resistor is the positive end. When you insert a resistor without rotating it or mirroring it, the positive terminal is the upper terminal, so the positive direction of current flow is downwards. If you rotate the resistor once in order to have a horizontal resistor symbol, the positive current flow is from right to left.

If your schematic contains errors, a window will open giving suggestions concerning what can be wrong. For instance, the ground symbol may be missing or a resistor value has not been specified. A slightly more tricky error has to do with the specification of component values. Be aware that a space between the value and the suffix is not allowed. If there is a space, the suffix will be ignored and the simulation will run with some unintended component values. A result window like shown in fig. 1.6 will still be shown but when you close this, a new window with an error log will appear. Also note that the suffix for 'milli' is m (or M - LTspice is case insensitive) while the suffix for 'Mega' is Meg (or meg).

When you have successfully completed the '.op' simulation and closed the window with the results, you can see currents and voltages in the circuit by moving the cursor to a component or a node and reading currents and voltages on the status bar at the bottom of the LTspice program window.

It may be useful to know at least the basics about the circuit description used by LTspice. The circuit is described by a netlist, and you can see the netlist using the command 'View  $\rightarrow$  SPICE Netlist'. You would notice the syntax for a resistor, for instance  $R_1$ : 'R1 V2 V1 40k'. Here you will recognize that the first node specified for the resistor (in this example 'V2') is the positive terminal of the resistor.

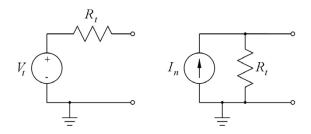

Figure 1.7: Thévenin equivalent (left) and Norton equivalent (right).

Thévenin – Norton equivalent circuits: For the circuit shown in fig. 1.1, you may define a Thévenin equivalent and a Norton equivalent as shown in fig. 1.7 (Hambley 2014). The Thévenin voltage  $V_t$  is the open-circuit voltage between the two rightmost terminals of the circuit in fig. 1.1 and the Norton current  $I_n$  is the short-circuit current between the two terminals. The Thévenin resistance  $R_t$  is the ratio between the Thévenin voltage and the Norton current, i.e.  $R_t = V_t/I_n$ . Also, the Thévenin resistance can be found as the resistance seen from the circuit terminals when the independent sources in the circuit are reset, i.e. with  $V_S = 0$  V. The Thévenin voltage has already been found by simulation of the circuit in fig. 1.4, and the result is given as the voltage 'V(v2)' in fig. 1.6, i.e.

$V_t = 2.4$  V. The short-circuit current is found by placing a short-circuit between the two rightmost terminals in the circuit. The short-circuit could simply be a wire, but in this case, the current in the wire is not listed in the output file from the '.op' simulation. You may also try to insert a resistor with the value 0, but running the simulation, you will find that the output file does not show the value of the current in this resistor. You may change the resistor value to a very small value (e.g. 1e-6), and in this case, the output file will show the current in the short-circuit resistor. Alternatively, you can model the short-circuit by a voltage source with a value of 0 V. In this case, the output file will show the current into the voltage source, and the voltage between the two terminals is 0 V, corresponding to a short-circuit. When running this simulation, you will find  $I_n = 0.5$  mA, and you can calculate  $R_t$  from  $R_t = V_t/I_n = 4.8$  k $\Omega$ . Alternatively,  $R_t$  can be found by simulation: Insert a current source  $I_1$  between the two rightmost terminals and simulate the voltage  $V_2$  across the current source with  $V_S = 0$  V. The current source is inserted as a component where you select 'current' in the component selection window. With the current flowing into the  $V_2$  terminal (rotate the current source symbol twice), the resistance is found as  $V_2/I_1$ , so if  $I_1$  is selected to be 1, the value of the voltage  $V_2$  is directly the value of the resistance between the terminals, i.e.  $R_t$ .

**Annotating simulation results on the schematic:** After having run a '.op' simulation, you may wish to display the simulation results directly on the schematic. Consider the circuit from fig. 1.4. For this circuit, we found the results shown in fig. 1.6. A very simple way to show these results on

the schematic is to use the 'Edit  $\rightarrow$  Text' command (toolbar symbol Aa, hotkey 'T') and just use normal copy and paste ('Ctrl-C', 'Ctrl-V') from the output file to the input window for the 'Edit  $\rightarrow$  Text' command. The result of doing so may look like shown in fig. 1.8. Notice that in this figure the font size has been specified to 1.0 when inserting the text (the default is 1.5), and the background colour has been changed to white using the command 'Tools  $\rightarrow$  Color Preferences' which opens a 'Color Palette Editor' for specifying the colours being used for schematics, netlists and waveforms.

Figure 1.8: The circuit from fig. 1.4 with the results of the '.op' simulation shown as text.

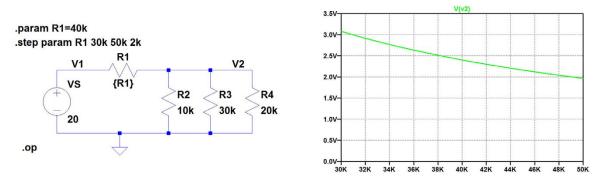

Figure 1.9: Dialogue box for entering simulation results on the schematic.

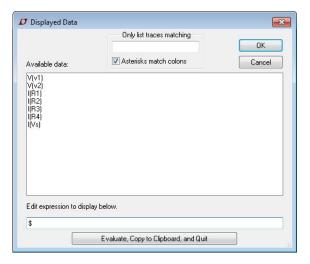

An alternative way to display specific simulation results is as follows: After having run the simulation, right click in an empty space on the schematic. This opens a command selection menu. Select the command 'View  $\rightarrow$  Place .op Data Label'. This opens a text box which can be placed at an appropriate location on the schematic. The text box just contains three question marks, ???. (An alternative way of opening this text box is to left click on a net label in the schematic ('V1' or 'V2' in fig. 1.8).) When you right click on the question marks, the dialogue box shown in fig. 1.9 opens. Suppose that we are interested in displaying the current in  $R_2$  and the power dissipated in  $R_2$ . The current is specified in the dialogue box, fig. 1.9, by replacing the \$ sign in the bottom line with

**Figure 1.10:** The circuit from fig. 1.4 with the current and the power for  $R_2$  shown on the schematic.

'I(R2)'. Adding a new text box in the same way lets you specify the expression 'I(R2)\*V(v2)' which will calculate the power in  $R_2$ . The resulting schematic may look like shown in fig. 1.10(a). You may find that the current and power need rounding off to integer  $\mu$ A and  $\mu$ W. This can be achieved using the function 'round(x)' in the specification window. Thus, for the current specify 'round(I(R2)\*1e6)/1e6' and for the power specify 'round(I(R2)\*V(v2)\*1e6)/1e6'. Then the resulting schematic looks like shown in fig. 1.10(b).

**Sweeping DC voltages and currents:** The simulations just shown give you values of voltages and currents in a specific operating point, i.e. for fixed values of all components in the system.

You can calculate the voltages and currents for other values of components simply by modifying your schematic and running the '.op' simulation again. However, there is also the possibility to sweep voltage sources and current sources over a range of voltages or currents. Assume that we would like to find currents and voltages in the circuit from fig. 1.1 for  $V_S$  varying between 10 V and 30 V. This is achieved by running a DC sweep simulation. Use the command 'Simulate  $\rightarrow$  Edit Simulation Cmd' and open the tab 'DC sweep'. This opens a dialogue box where you can specify your signal source and the sweep range. Also the increment must be specified. Select for instance an increment of 1 V. When you have completed the specification for  $V_S$ , you click 'OK'. This opens a command line which can now be placed on the schematic by the cursor. Insert the command by a left mouse click or by typing 'Return'. The command is shown in the schematic as '.dc VS 10 30 1'. You may observe that your previous simulation command, '.op', is now modified to ';op'. This modification turns it into a comment, and only the new simulation command is executed when you run the simulation. Next, the simulation is run by the command 'Simulate  $\rightarrow$  Run' or by using the 'Run'-symbol  $\nearrow$  on the toolbar.

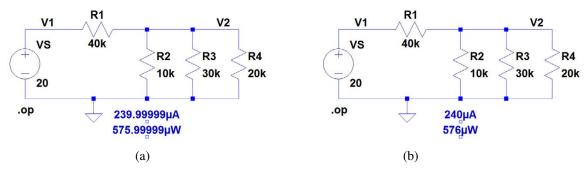

Assuming that there are no errors in the circuit and in the simulation command, a new window opens for showing plots of currents and/or voltages. The x-axis shows the voltage range specified for  $V_S$ , but initially the plot window is empty. The voltages and/or currents to be shown in the plot window can be selected in different ways: With the plot window active, you can use the command 'Plot settings  $\rightarrow$  Add trace' or the command 'Plot settings  $\rightarrow$  Visible Traces'. The command 'Visible Traces' is also available with the schematic window active ('View  $\rightarrow$  Visible Traces') and on the toolbar, symbol  $\rightleftharpoons$ . You may notice that the 'Add trace' command works in a different way than the 'Visible Traces' command. With the 'Add trace' command, you left click on the traces that you want to see, and they are all listed in the window in the bottom of the dialogue box. With the 'Visible Traces' command, you select only one trace with a left mouse click. If you want more than one variable, use 'Ctrl-left click' to turn on and off the traces to display. The 'Add trace' command is also available by the hotkey 'Ctrl-A'.

An alternative method for selecting traces is to point at nodes in the schematic for voltages and at components for currents. This turns the cursor into a red pointer, , an oscilloscope probe, for the voltages and a current probe for the currents, . Note that a red arrow in the current probe also shows the positive direction of current flow. Just left click at the trace to be added and it will appear in the plot window. A double click implies that only the selected trace is shown. Also, you may note that by pointing to a wire and pressing the 'Alt' key, you can select the current in a wire. The voltage difference between two nodes can also be displayed using the voltage probe: Left click and hold on one node and drag the mouse to another node. A red voltage probe will appear at the first node and a black probe at the second node. Finally, when you hold down the 'Alt' key while pointing to a device (e.g. a resistor), the cursor turns into a thermometer and the resulting plot traces the power dissipated in the device.

Figure 1.11: Plot of DC sweep simulation for circuit example from fig. 1.4 using the LTspice default setup of colours.

The waveform plot can be copied to the clipboard in the same way as the schematic: Use the command 'Tools  $\rightarrow$  Copy bitmap to Clipboard' and then paste the waveform plot into another program. The resulting plot showing the voltage  $V_2$  and the current through  $R_1$  may look like shown in fig. 1.11. You may find that the blue trace ('I(R1)') is difficult to see on the black background. You can change the colour of the trace by pointing to the trace name above the plot and right clicking. This opens a window where you can select another colour. Alternatively, you may change the background colour of the plot pane by the command 'Tools  $\rightarrow$  Color Preferences' which opens a dialogue window where you can specify colours for waveforms, schematics and netlists. Also note that if you left click instead of right click on the trace name, a cursor appears which will follow the trace when you move it around by the mouse. This is useful for finding values of the current for specific values of the voltage  $V_S$ .

Once you have closed the plot window, you can re-open it by the command 'View  $\rightarrow$  Visible Traces', toolbar symbol  $\stackrel{\text{left}}{\cong}$ . If you have applied the command 'Plot Settings  $\rightarrow$  Save Plot Settings' before closing the plot window, it will re-open showing the selected traces, otherwise just with an empty plot window.

Another way of finding values of the currents and voltages for specific values of  $V_S$  is to use the command 'File  $\rightarrow$  Export' from the plot window. This opens a window for selecting waveforms to export, and when you have selected the desired waveforms and click 'OK', a '.txt' file is generated with the waveforms given in tabular form. This file can also be opened by LTspice. Use 'File  $\rightarrow$

| Exported file with selected traces from DC sweep simulation |               |                |  |

|-------------------------------------------------------------|---------------|----------------|--|

| vs V(v2) I(R1)                                              |               |                |  |

| 1.000000000000000e+001                                      | 1.200000e+000 | -2.200000e-004 |  |

| 1.100000000000000e+001                                      | 1.320000e+000 | -2.420000e-004 |  |

| 1.200000000000000e+001                                      | 1.440000e+000 | -2.640000e-004 |  |

| 1.300000000000000e+001                                      | 1.560000e+000 | -2.860000e-004 |  |

| 1.400000000000000e+001                                      | 1.680000e+000 | -3.080000e-004 |  |

| 1.500000000000000e+001                                      | 1.800000e+000 | -3.300000e-004 |  |

| 1.600000000000000e+001                                      | 1.920000e+000 | -3.520000e-004 |  |

| 1.700000000000000e+001                                      | 2.040000e+000 | -3.740000e-004 |  |

| 1.800000000000000e+001                                      | 2.160000e+000 | -3.960000e-004 |  |

| 1.900000000000000e+001                                      | 2.280000e+000 | -4.180000e-004 |  |

| 2.000000000000000e+001                                      | 2.400000e+000 | -4.400000e-004 |  |

| 2.100000000000000e+001                                      | 2.520000e+000 | -4.620000e-004 |  |

| 2.200000000000000e+001                                      | 2.640000e+000 | -4.840000e-004 |  |

| 2.300000000000000e+001                                      | 2.760000e+000 | -5.060000e-004 |  |

| 2.400000000000000e+001                                      | 2.880000e+000 | -5.280000e-004 |  |

| 2.500000000000000e+001                                      | 3.000000e+000 | -5.500000e-004 |  |

| 2.600000000000000e+001                                      | 3.120000e+000 | -5.720000e-004 |  |

| 2.700000000000000e+001                                      | 3.240000e+000 | -5.940000e-004 |  |

| 2.800000000000000e+001                                      | 3.360000e+000 | -6.160000e-004 |  |

| 2.900000000000000e+001                                      | 3.480000e+000 | -6.380000e-004 |  |

| 3.000000000000000e+001                                      | 3.600000e+000 | -6.600000e-004 |  |

Figure 1.12: Table with results of DC sweep simulation for circuit example from fig. 1.4.

Open' (or on the toolbar) and select 'Files of type: all files'. In the file list, open the '.txt' file with the name corresponding to your circuit. The resulting table may look like shown in fig. 1.12.

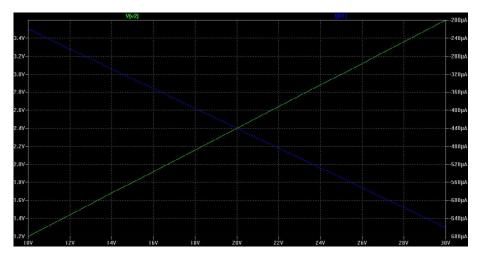

Sweeping resistor values: Instead of showing variations in the circuit of fig. 1.1 when sweeping the voltage source  $V_S$  you might be interested in analyzing the circuit when sweeping a resistor value, e.g. the value of  $R_1$ . This can be achieved by specifying the value of  $R_1$  as a variable parameter. To do so, the specification for  $R_1$  should be changed on the resistor symbol. Instead of specifying the value 40k, the value must be specified to be '{R1}' (remember to include the curly brackets '{}'). Now you can specify a sweep range for the parameter 'R1' by inserting a '.step' command: Click 'Edit  $\rightarrow$  SPICE Directive' (or 'P' on the toolbar), and a dialogue window appears in which you can type a command. Insert the command '.step param R1 30k 50k 2k'. This will sweep the value of  $R_1$  from 30 k $\Omega$  to 50 k $\Omega$  in steps of 2 k $\Omega$ . Finally, run a '.op' simulation.

If your circuit does not have any errors, the simulation will open a plot window with the resistance range of  $30 \text{ k}\Omega$  to  $50 \text{ k}\Omega$  as the horizontal axis. You may select voltages and currents to be displayed in the same way as for the DC sweep simulations. Fig. 1.13 shows the schematic from fig. 1.4 with the '.step' command inserted, and it shows the resulting waveform plot of  $V_2$ . Here, the colour preferences of the waveform plot and the schematics have been modified to get a white background and black axes on the waveform plot. Also, rather than using the autorange scaling of the vertical axis, the axis has been modified to the range from 0 V to 3.5 V. This can be done by the command

**Figure 1.13:** Simulation of sweep of resistor  $R_1$  from fig. 1.1.

'Plot settings  $\rightarrow$  Manual Limits' or by moving the mouse cursor over the axis and left clicking. In fig. 1.13 (and in subsequent figures showing simulation plots), the font size of the labels on the axes has been increased using the command 'Tools  $\rightarrow$  Control Panel' and the tab 'Waveforms' where the font has been changed to Arial and the fontsize to 18 points.

In a waveform plot, you can insert text and other annotations (e.g. cursor position) using the command 'Plot Settings  $\rightarrow$  Notes & Annotations'.

In the plot window, you can also zoom in on details simply by clicking and dragging to define a box using the left mouse button.

If you want to run a simulation with just one value for a variable parameter (R1 in fig. 1.13), then instead of the '.step' command, you can specify the value of R1 using a '.param' command: Insert the SPICE Directive '.param R1=40k' to run a simulation with  $R_1=40~\rm k\Omega$  and delete the '.step' command or edit it into a comment by inserting an asterix (\*) as the first character or by ticking 'Comment' in the editing window. If you do not disable the '.step' command, the simulation will run this command regardless of the '.param' specification.

The '.step param' command is a very useful command for design iterations. By defining relevant design parameters as variable parameters and stepping the values over a suitable range, you can quickly examine the influence of a parameter on the circuit characteristics. Problems 1.2 on page 38 and 1.5 on page 39 are examples of this.

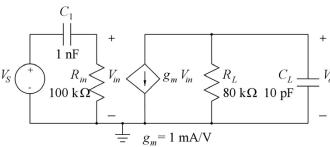

#### Example 1.2: A transconductance amplifier.

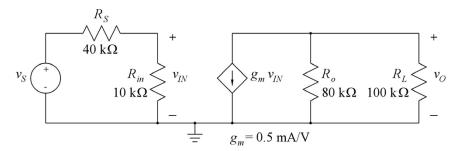

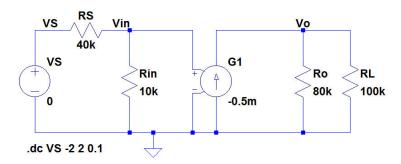

The next example is a circuit containing a voltage controlled current source as shown in fig. 1.14. Essentially, this is an inverting transconductance amplifier with an input resistance  $R_{in}$ , an output resistance  $R_o$  and a transconductance  $g_m$ . In fig. 1.14, a load resistor  $R_L$  and a signal source  $V_S$  with a source resistance  $R_S$  is connected to the amplifier.

Figure 1.14: An inverting transconductance amplifier.

Figure 1.15: LTspice schematic for the inverting transconductance amplifier.

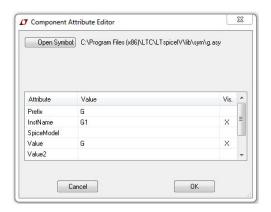

In this circuit, there is a new type of component, the controlled current source. LTspice has, like other Spice programs (Tuinenga 1995; Vladimirescu 1994), a voltage controlled current source as a standard component with the circuit designator G. The schematic drawn in LTspice is shown in fig. 1.15. The LTspice symbol for the controlled current source explicitly shows the controlling voltage as input terminals to the component symbol. The controlled current source is edited by right clicking on the symbol. This opens a 'Component Attribute Editor' as shown in fig. 1.16. By double clicking on the values for 'InstName' and 'Value', the values can be changed to the values shown in fig. 1.15. Alternatively, just right click on the device number (e.g. G1) and the value G to edit them

Figure 1.16: The window for editing the specifications of the voltage controlled current source.

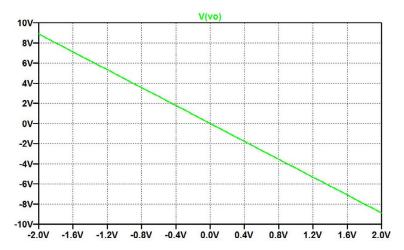

**Figure 1.17:** Plot of  $v_O$  versus  $v_S$  for the inverting amplifier.

to the desired values in the same way as editing the value of a resistor or a DC current source. By editing the simulation command, you may now run a DC sweep simulation, e.g. sweeping  $v_S$  from -2 V to +2 V. The resulting plot of  $v_O$  versus  $v_S$  may look like shown in fig. 1.17.

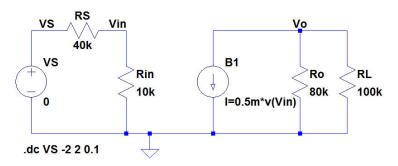

The arbitrary behavioural source: LTspice also provides an alternative to the voltage controlled current source. This is an 'Arbitrary behavioural current source', device type 'bi' in the component selection. The same device can be used for both a voltage controlled current source and a current controlled current source. Fig. 1.18 shows the circuit from fig. 1.14 redrawn with the 'bi' symbol. Notice the definition line for the current source: 'I=0.5m\*v(Vin)'. You need to specify the controlling voltage as 'v(Vin)', not just 'Vin', otherwise you will receive an error message. Also note that \* is the character indicating multiplication.

In fig. 1.18, the symbol for the controlled current source is a circle, exactly like the symbol for an

Figure 1.18: LTspice schematic for the inverting transconductance amplifier using an arbitrary behavioural current source.

Figure 1.19: The inverting amplifier with a diamond shaped symbol for the arbitrary behavioural current source.

independent current source. Often in the literature, controlled sources are represented by a diamond shaped symbol to distinguish them from the independent sources (Hambley 2014; Sedra & Smith 2011). You may actually edit the symbol for the controlled current source using the symbol editor in LTspice. When you are in the 'Component Attribute Editor' (fig. 1.16), you click 'Open Symbol' to enter the symbol editor where you can redraw the shape of the symbol.

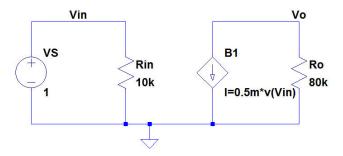

In fig. 1.19, the transconductance amplifier is redrawn with a diamond shaped symbol, and the load resistor  $R_L$  and source resistor  $R_S$  are omitted. The circuit shown has only linear components, and it is easy to see that the input resistance is  $R_{in} = 10 \text{ k}\Omega$  and the output resistance is  $R_o = 80 \text{ k}\Omega$ . The open circuit voltage gain  $A_{voc}$  can be calculated from  $A_{voc} = -g_m \times R_o = -40 \text{ V/V}$ , where  $g_m = 0.5 \text{ mA/V}$  is the transconductance of the voltage controlled current source. These values can also be found by simulation: With an input voltage of  $v_S = v_{IN} = 1 \text{ V}$ , the output voltage is  $v_O = A_{voc} \times 1 \text{ V}$ , so the simulated value of the output voltage directly gives the value of  $A_{voc}$ . By changing the input signal to a current source of 1 A, the value of the input voltage is  $R_{in} \times 1 \text{ A}$ , so the simulated value of the input voltage directly gives the value of the output voltage is  $R_o \times 1 \text{ A}$ , so the simulated value of the output voltage directly gives the value of the output voltage is  $R_o \times 1 \text{ A}$ , so the simulated value of the output voltage directly gives the value of the output voltage is  $R_o \times 1 \text{ A}$ , so the simulated value of the output voltage directly gives the value of  $R_o$ .

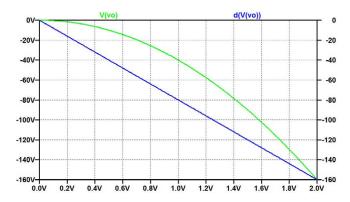

**Nonlinear controlled current source:** Next, we assume that the voltage controlled current source is given by a nonlinear relation,  $I = 0.5 \text{ mA/V}^2 \times v_{IN}^2$  for  $v_{IN} \ge 0 \text{ V}$ . The specification for 'B1' in fig. 1.19 must then be modified to 'I=0.5m\*v(Vin)\*\*2'. Observe the double asterix (\*\*) for raising to power of 2. With  $v_{IN} = 1 \text{ V}$ , the '.op' simulation still results in  $v_O = -40 \text{ V}$ , but a DC sweep of  $v_{IN}$  from 0 V to 2 V shows the nonlinear relation between  $v_O$  and  $v_{IN}$ , see the green curve in fig. 1.20.

For this amplifier, the voltage gain is not just  $v_O/v_{IN}$ . Rather, the voltage gain is defined as the small signal gain  $A_{voc} = \partial v_O/\partial v_{IN}$  calculated in the bias point of the amplifier. For an input bias voltage of  $V_{IN} = 1$  V, we find  $A_{voc} = \partial v_O/\partial v_{IN} = -R_o \times 2 \times 0.5$  mA/V<sup>2</sup> ×  $V_{IN} = -80$  V/V. Obviously, the

Figure 1.20: Plot of  $v_O$  versus  $v_S$  for the inverting amplifier with a nonlinear voltage controlled current source.

gain depends on the bias value of the input voltage. The voltage gain is also seen as the slope of the nonlinear relation between  $v_O$  and  $v_{IN}$ . This slope can be displayed directly in the plot window: When you click on the command 'Plot Settings  $\rightarrow$  Add trace' (or hotkey 'Ctrl-A'), a window opens for specifying traces to plot. The bottom line in this window lets you enter an expression to add. A large selection of mathematical operations is available (see the 'Help' menu), including the derivative of a variable with respect to the x-axis variable. The function 'd(V(vo))' will give you the derivative of the output voltage with respect to the input voltage. The resulting plot is the blue line in fig. 1.20 from which you can see that  $A_{voc} = -80$  V/V as expected for  $V_{IN} = 1$  V.

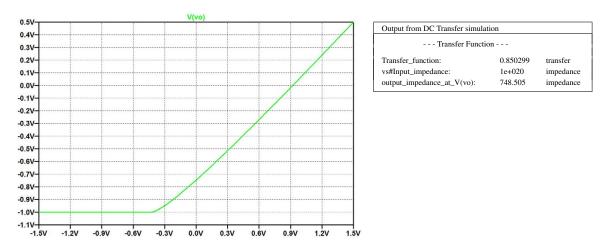

| Output from DC Transfer simulation |       |           |  |  |

|------------------------------------|-------|-----------|--|--|

| Transfer Function                  |       |           |  |  |

| Transfer_function:                 | -80   | transfer  |  |  |

| vs#Input_impedance:                | 10000 | impedance |  |  |

| output_impedance_at_V(vo):         | 80000 | impedance |  |  |

Figure 1.21: Output from '.tf' simulation of the circuit from fig. 1.19.

LTspice has another simulation command which will directly give you the small signal transfer function at DC, the 'DC Transfer' simulation. Use the command 'Simulate  $\rightarrow$  Edit Simulation Command' and choose the tab 'DC Transfer'. Here you specify the output and the source. For the circuit of fig. 1.19, the output is 'v(Vo)' (not just 'Vo') and the source is 'VS'. The resulting simulation command is '.tf v(Vo) VS' and after running the simulation (with 'I=0.5m\*v(Vin)\*\*2'), a window opens with the information shown in fig. 1.21.

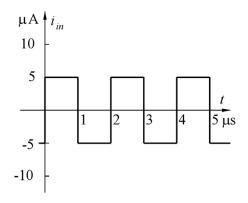

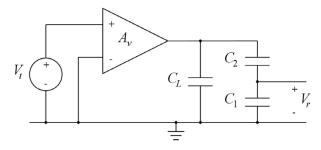

#### Example 1.3: A current amplifier.

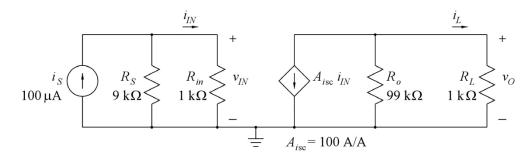

The final example in this tutorial is a current amplifier as shown in fig. 1.22. The gain element in this circuit is a current controlled current source. The current amplifier has an input resistance  $R_{in}$ , a short circuit current gain  $A_{isc}$  and an output resistance  $R_o$ .

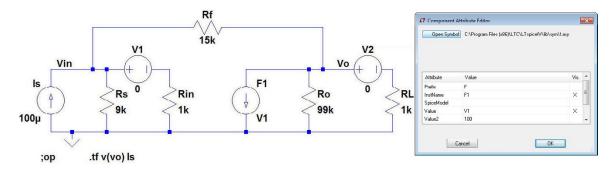

Figure 1.22: An inverting current amplifier.

Figure 1.23: LTspice schematic for the inverting current amplifier.

A simple examination of the circuit shows an inverting current gain from the input signal  $i_S$  to the current  $i_L$  in the load resistor of  $A_{isc}$  multiplied by the current divider ratios at the input side and the output side. With the values shown in fig. 1.22, we find  $i_L/i_S = -89.1$  A/A. For  $i_S = 100$   $\mu$ A, we get an output current  $i_L = -8.91$  mA and an output voltage of  $v_O = -8.91$  V.

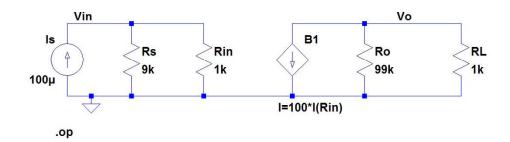

In LTspice, the current controlled current source is described either by the device type 'F' or by the 'Arbitrary behavioural current source', device type 'bi' in the component selection. Fig. 1.23 shows the schematic drawn with the arbitrary behavioural current source (using a diamond shaped symbol). Obviously, when examining fig. 1.22, the current is controlled by the current through  $R_{in}$ , so an immediate specification for B1 would be 'I=100\*I(Rin)' as shown in fig. 1.23. Running a '.op' simulation indeed also results in the expected values of  $i_L$  and  $v_O$ .

But running a '.tf' simulation (see page 32) with 'Is' as the source and 'v(Vo)' as the output gives a transfer function of 0 which is obviously not correct. The value to expect is  $v_O/i_S = -8910$  V/A. The input resistance and the output resistance from the '.tf' simulation are shown as 900 and 990, respectively, which is as expected since the input side is a parallel connection of 1 k $\Omega$  and 9 k $\Omega$ . Trying a '.tf' simulation with 'I(RL)' as the output also results in a transfer function of 0.

**Figure 1.24:** LTspice schematic for the inverting current amplifier with voltage sources in series with  $R_{in}$  and  $R_L$  and altered specification for B1.

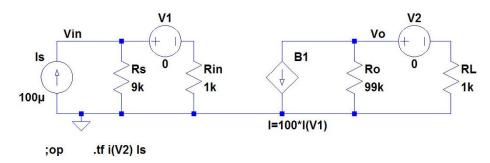

The reason for these errors is that some of the analyses in LTspice (e.g. '.tf' and '.ac' (see tutorial 2)) require that a current is specified as a current through a voltage source as described on page 20.

Fig. 1.24 shows the circuit from fig. 1.23 redrawn with DC voltage sources of 0 V in series with  $R_{in}$  and  $R_L$  and B1 specified as 'I=100\*I(V1). The '.op' simulation still provides the correct result, and now also both '.tf' simulations with 'v(Vo)' and 'i(V2)' as output show the expected gain. The input resistance is found from both '.tf' simulations, but the output resistance is found only from the simulation with 'v(Vo)' as the output.

**Figure 1.25:** LTspice schematic for the inverting current amplifier with a feedback resistor  $R_f$ .

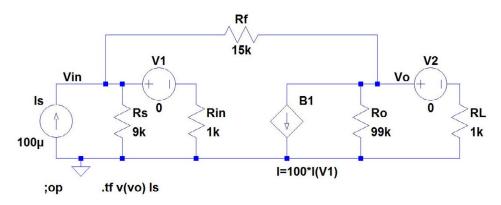

Now, let us connect a feedback resistor  $R_f$  of 15 k $\Omega$  between output and input as shown in fig. 1.25, shunt - shunt feedback (Sedra & Smith 2011). With this feedback resistor, the amplifier is turned into a transresistance amplifier. With a very large current gain  $A_{isc}$ , we would expect a transresistance equal to  $-R_f$  and small values of input and output resistance. The '.tf' simulation with  $v_O$  as the output shows a gain (transresistance) of -12.6 k $\Omega$ , an input resistance of 136  $\Omega$  and an output resistance of 149  $\Omega$  (including  $R_s$  and  $R_L$ ). Increasing  $A_{isc}$  to 1000, we find a gain very close to -15 k $\Omega$  and input and output resistances in the range of 1 to 2  $\Omega$ .

Next, see what happens if we change the specification of the current controlled current source to 'I=100\*I(Rin)'. Then we find that neither the '.op' simulation, nor the '.tf' simulations will run. They all return the error message 'Analysis failed: Iteration limit reached'. This shows that LTspice is unable to find the bias point from the '.op' simulation when the current is not specified as the current through a voltage source. In other examples, the operating point may be found but with reduced precision if the current is specified as the current in a resistor. Examples of such circuits are given in problems P1.3 on page 38 and P1.4 on page 39.

The lesson learned from this example is: The controlling current for a current controlled voltage source or a current controlled current source must be the current through a voltage source. Insert a DC voltage source of 0 V in series with the device carrying the controlling current and use the current in this voltage source as the controlling current.

Figure 1.26: Circuit from fig. 1.25 redrawn with a current controlled current source instead of an arbitrary controlled current source.

This is also the way to specify a controlling current when using the current controlled current source with circuit designator F. Fig. 1.26 shows the circuit from fig. 1.25 redrawn with the device 'f' instead of 'bi' and also shows the specification window for 'f'. In this window, the name of the DC voltage source for the controlling current must be specified in the line 'Value', and the current gain must be specified in the line 'Value2'.

By now you should be well prepared for analyzing resistive circuits with different kinds of voltage sources and current sources such as the examples given in the following problems.

#### Hints and pitfalls

- The suffix for 'milli' is 'm'. The suffix for 'Mega' is 'meg'. After the suffix, you may insert the unit (e.g. A for ampere). An alternative suffix is 'e' followed by the power of 10, e.g. 'e-3' for 'milli'.

- Do NOT insert a space between a component value and the suffix or unit.

- Always define a ground node in your circuit.

- Many commands can be selected either via a command and subcommand (e.g. 'Edit → Resistor'), a toolbar symbol (e.g.

, or a hotkey (e.g. R). The assignment of hotkeys can be seen using the command 'Tools → Control Panel → Drafting Options → Hotkeys'.

- The commands 'Drag', 'Move', 'Duplicate' and 'Delete' work not only on single symbols.

When you have activated one of the commands, you can define a box by clicking and dragging using the left mouse button. The command works on the entire contents of the box.

- When you have several identical components in your circuit, it is convenient to edit just one instance of the component to the correct value and then use the 'Duplicate' command (F6), rather than inserting and editing each component individually.

- See problem 1.8 on page 41 for more hints on drawing schematics.

- When you move the mouse cursor to a component symbol or text, the status bar at the bottom of the LTspice program window gives information about editing options.

- Colour preferences can be edited for both schematics and waveforms using the command 'Tools → Color Preferences'.

- Font sizes on schematics and waveform plots can be modified using the command 'Tools

→ Control Panel' and the appropriate tab (e.g. 'Drafting Options' or 'Waveforms').

- If you have closed a window with results (e.g. from a '.op' simulation or a waveform plot),

you can re-open it by the command 'View → Visible Traces', toolbar symbol \( \begin{align\*}{2} \end{align\*} \).

- In a waveform plot, you can zoom in on details by clicking and dragging to define a box using the left mouse button.

- Text and other annotations (e.g. cursor position) can be placed in a simulation plot using the command 'Plot Settings → Notes & Annotations'.

- Schematics and waveform plots can be copied to the clipboard with the command 'Tools

→ Copy bitmap to Clipboard' and then pasted into another program (e.g. Microsoft Word).

- The controlling current for a current controlled voltage source or a current controlled current source must be the current through a voltage source. Insert a DC voltage source of 0 V in series with the device carrying the controlling current and use the current through this voltage source as the controlling current.

#### References

Hambley, AR. 2014, *Electrical Engineering, Principles and Applications*, Sixth Edition, Pearson Education Ltd., Harlow, UK.

Sedra, AS. & Smith, KC. 2011, *Microelectronic Circuits*, International Sixth Edition, Oxford University Press, New York, USA.

Tuinenga, PW. 1995, *Spice: A Guide to Circuit Simulation and Analysis Using PSpice*, Third Edition, Prentice Hall, Upper Saddle River, USA.

Vladimirescu, A. 1994, *The SPICE book*, First Edition, John Wiley & Sons, Hoboken, USA.

#### **Problems**

#### 1.1

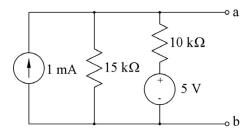

Figure P1.1

For the circuit shown in fig. P1.1, find the Thévenin voltage  $V_t$  and the Thévenin resistance  $R_t$ . A load resistor of  $R_L = 3 \text{ k}\Omega$  is now connected between the terminals a and b. Find the power dissipated in  $R_L$ .

1.2

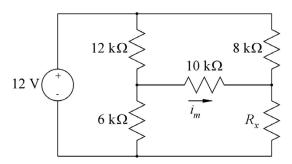

Figure P1.2

For the circuit shown in fig. P1.2, determine the value of resistor  $R_x$  so that the current  $i_m$  in the 10 k $\Omega$  resistor is 30  $\mu$ A.

1.3

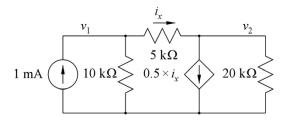

Figure P1.3

For the circuit shown in fig. P1.3, determine the value of the voltages  $v_1$  and  $v_2$  and the current  $i_x$ .

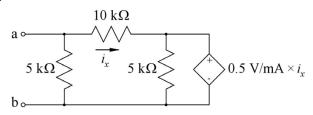

Figure P1.4

For the circuit shown in fig. P1.4, find the equivalent resistance looking into terminals a - b.

1.5

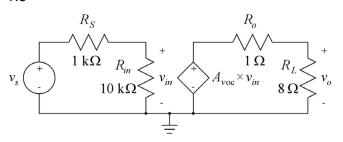

Figure P1.5

For the circuit shown in fig. P1.5, find the value of the gain  $A_{voc}$  which gives an output power in  $R_L$  of 1 W when the signal voltage  $v_s$  is 50 mV. With this value of  $A_{voc}$ , plot the output power versus the input voltage for  $v_s$  in the range from 0 mV to 100 mV.

#### Top master's programmes

- 33<sup>rd</sup> place Financial Times worldwide ranking: MSc International Business

- 1st place: MSc International Business

- 1st place: MSc Financial Economics

- 2<sup>nd</sup> place: MSc Management of Learning

- 2<sup>nd</sup> place: MSc Economics

- 2<sup>nd</sup> place: MSc Econometrics and Operations Research

- 2<sup>nd</sup> place: MSc Global Supply Chain Management and Change

Sources: Keuzegids Master ranking 2013; Elsevier 'Beste Studies' ranking 2012; Financial Times Global Masters in Management ranking 2012

> Maastricht University is the best specialist university in the Netherlands

Visit us and find out why we are the best! Master's Open Day: 22 February 2014

www.mastersopenday.nl

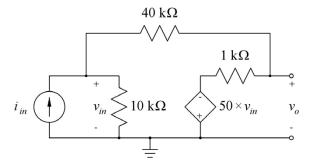

Figure P1.6

1.7

Figure P1.7

The circuit shown in fig. P1.6 is a transresistance amplifier built from an inverting voltage amplifier with an input resistance of 10 k $\Omega$ , an output resistance of 1 k $\Omega$  and an open circuit voltage gain of -50 V/V and a feedback resistor with a value of 40 k $\Omega$ . Find the open circuit transresistance  $R_{moc}$ , the input resistance  $R_{in}$  and the output resistance  $R_o$  of the resulting transresistance amplifier.

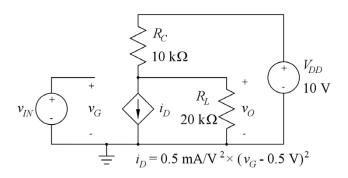

Fig. P1.7 shows a nonlinear transconductance amplifier. Find the values of bias voltages and currents for an input bias voltage (quiescent voltage) of  $V_{IN} = 1.0 \text{ V}$ . Plot the output voltage  $v_O$  for the input voltage in the range from 0.5 V to 1.8 V. Find the small signal voltage gain  $v_O/v_{in}$  for an input bias voltage of  $V_{IN} = 1.0 \text{ V}$  and plot the small signal voltage gain as a function of the input bias voltage for the input bias voltage in the range from 0.5 V to 1.8 V.

Figure P1.8

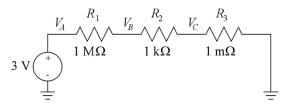

Fig. P1.8 shows a series connection of three resistors and a voltage source.

Try three different ways of drawing the schematic:

- (1): Insert the components and draw the connections between them.

- (2): Insert the components (including the ground symbols) and draw an unbroken wire (hotkey 'F3') from leftmost ground symbol across the components to rightmost ground symbol.

- (3): Insert the ground symbols, draw an unbroken wire between them, and then insert the component directly on top of the wire.

Observe how LTspice 'cleans up' the wiring.

Find the voltages  $V_A$ ,  $V_B$  and  $V_C$ .

#### **Answers**

- 1.1:  $V_t = 9 \text{ V}$ ;  $R_t = 6 \text{ k}\Omega$ ;  $P_{R_L} = 3 \text{ mW}$ .

- 1.2:  $R_x = 3.31 \text{ k}\Omega$ .

- 1.3:  $v_1 = 6 \text{ V}$ ;  $v_2 = 4 \text{ V}$ ;  $i_x = 0.4 \text{ mA}$ .

- 1.4:  $R_{ab} = 3.387 \text{ k}\Omega$ .

- 1.5:  $A_{voc} = 70 \text{ V/V}.$

- 1.6:  $R_{moc} = -36.28 \text{ k}\Omega$ ;  $R_{in} = 744 \Omega$ ;  $R_o = 90.7 \Omega$ .

- 1.7: Bias point:  $I_D = 0.125$  mA;  $I_C = 0.417$  mA;  $I_L = 0.292$  mA;  $V_O = 5.83$  V. Small signal voltage gain with  $V_{IN} = 1.0$  V:  $v_O/v_{in} = -3.33$  V/V.

- 1.8:  $V_A = 3.0000 \text{ V}$ ;  $V_B = 2.997 \text{ mV}$ ;  $V_C = 2.997 \text{ nV}$ .

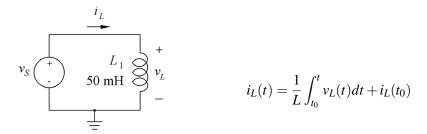

# Tutorial 2 – Circuits with Capacitors and Inductors

This tutorial introduces the fundamentals of transient simulations and AC simulations. After having completed the tutorial, you should be able to

- specify a transient simulation in LTspice.

- specify an AC simulation in LTspice.

- use the simulation plots for finding circuit properties such as time constants and -3 dB frequencies.

- use simple components specified by a '.model' directive.

- specify initial conditions for capacitors and inductors.

#### Example 2.1: An RC network.

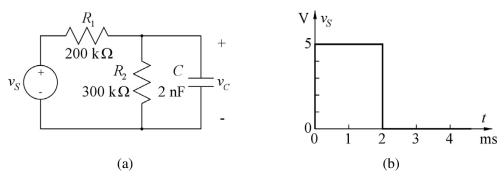

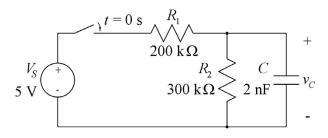

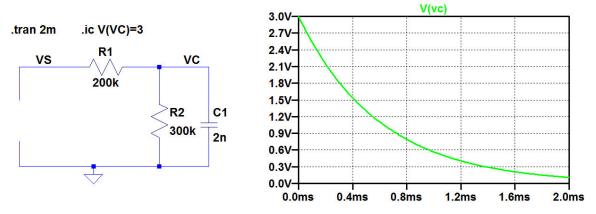

The first example is a simple RC network with two resistors and a capacitor as shown in fig. 2.1:

**Figure 2.1:** RC network (a) and input voltage  $v_S$  to the network (b).

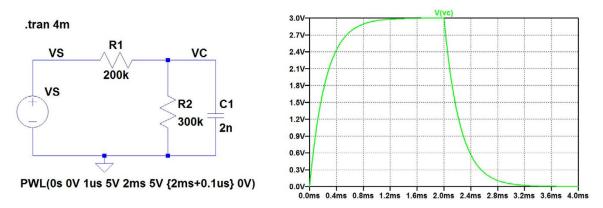

**Transient response:** Let us assume that the voltage source  $v_S$  is a time varying voltage as shown in fig. 2.1(b). The voltage jumps from 0 V to a value of 5 V at time t = 0 and returns to 0 V at the time t = 2 ms. This will cause the capacitor to charge and discharge. For a simulation of the charging and discharging, we will run a transient simulation and specify the voltage source  $v_S$  as a time varying voltage. The circuit is drawn in LTspice using the selection of editing commands as in tutorial 1. The capacitor is available both as a command, 'Edit  $\rightarrow$  Capacitor', as a toolbar symbol  $\stackrel{+}{\Rightarrow}$ , and as a hotkey 'C'.

When specifying the voltage source  $v_S$ , you point to the centre of the symbol. This turns the cursor into a hand  $\blacksquare$ . A right mouse click opens a window for specifying the voltage source. In this window, left click on 'Advanced'. This opens a dialogue box where you may select time varying functions, e.g. PWL, piecewise linear. A series of boxes for entering times and values will appear. Notice that the voltage cannot be changed abruptly, so the vertical edges from fig. 2.1(b) have to have a certain slope. Corresponding to the timing in fig. 2.1(b), you may enter time1=0s, value1=0V, time2=0.1us, value2=5V, time3=2ms, value3=5V, time4=2.0001ms, value4=0V. In this way, the voltage changes from 0 V to 5 V in 0.1  $\mu$ s. An alternative to specifying time4 as 2.0001ms is to specify time4={2ms+0.1us}. Remember to include the curly brackets '{}', otherwise you will receive an error message and the simulation will not run. Also note that you may include the units ('s' for seconds and 'V' for volts). This makes it easier to read the specification shown on

## Empowering People. Improving Business.

BI Norwegian Business School is one of Europe's largest business schools welcoming more than 20,000 students. Our programmes provide a stimulating and multi-cultural learning environment with an international outlook ultimately providing students with professional skills to meet the increasing needs of businesses.

BI offers four different two-year, full-time Master of Science (MSc) programmes that are taught entirely in English and have been designed to provide professional skills to meet the increasing need of businesses. The MSc programmes provide a stimulating and multicultural learning environment to give you the best platform to launch into your career.

- · MSc in Business

- · MSc in Financial Economics

- MSc in Strategic Marketing Management

- MSc in Leadership and Organisational Psychology

www.bi.edu/master

the schematic. The specification is shown unless you untick the box for 'Make this information visible on schematic'. This is not recommended. The specification does take up some space on the schematic, but you may move this information to a convenient place in the schematic using the 'Move' or 'Drag' command.

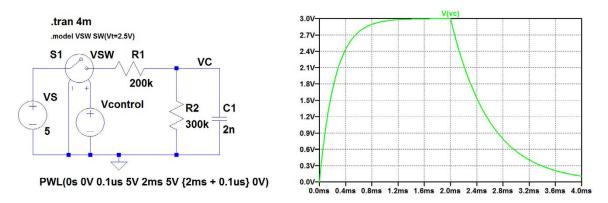

Next, you should specify the simulation. Use the command 'Simulate → Edit Simulation Cmd' and open the tab 'Transient'. For a simulation of the charging and discharging of the capacitor, you can run the simulation starting at time t=0 s and stopping at the time specified in the box for 'Stop Time'. Inserting a stop time of 4 ms, the transient simulation will show both the charging and the discharging. The circuit is now ready for simulation. If there are no errors, the simulation will open a plot window with a time axis and by pointing to 'VC' on the schematic (the red pointer, ), the capacitor voltage  $v_C$  will be shown in the plot window. Fig. 2.2 shows both the schematic drawn in LTspice and the resulting plot window.

Figure 2.2: LTspice schematic and simulation results for the circuit in fig. 2.1.

It is obvious that the charging and discharging takes place with the same time constant. For the charging, a simple analysis of the circuit gives

$$v_C = V_0 \times (1 - \exp(-t/\tau)) \tag{2.1}$$

$$V_0 = V_s \times \frac{R_2}{R_1 + R_2} = 3 \text{ V}$$

(2.2)

$$V_0 = V_s \times \frac{R_2}{R_1 + R_2} = 3 \text{ V}$$

$$\tau = \frac{1}{(R_1 \parallel R_2) \times C} = 240 \text{ }\mu\text{s}$$

(2.2)

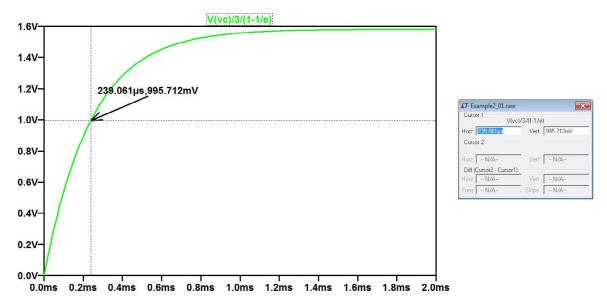

The time constant can also be found from the simulation of the charging. From  $v_C = V_0 \times (1 - 1)$  $\exp(-t/\tau)$ ), we find that at  $t=\tau$ , the voltage is  $V_0(1-1/e)$ . Therefore, if we scale the output by a factor of  $[V_0(1-1/e)]^{-1}$ , the scaled voltage will be 1 V when  $t=\tau$ . By using the command 'Plot Settings → Add trace' (or the hotkey 'Ctrl-A'), you can open a window for selecting traces. In the bottom line, you can enter 'Expression(s) to add'. In this case, enter 'V(vc)/3/(1-1/e)' and click

Figure 2.3: Plot window with scaled output for finding the time constant.

'OK'. Notice that the waveform editor in LTspice recognizes e (or E) as the base for the natural logarithm. This generates a new trace in the plot, scaled so that the voltage is 1 V for  $t = \tau$ . You can find this time by left clicking on the trace name above the plot to activate a cursor which follows the trace when you move it around by the mouse. Also, a window opens showing the position of the cursor, so you just move the cursor until the vertical position is 1 V and read the horizontal position of the cursor as the value of  $\tau$ .

Fig. 2.3 shows the plot window with the scaled capacitor voltage. In this figure, the x-axis has been scaled to show only the interval from 0 to 2 ms. Also, the grid has been turned off by the command 'Plot Settings  $\rightarrow$  Grid' (or 'Ctrl-G') in order to make the cursor more visible. The figure also shows the window with the coordinates for the position of the cursor. This window can be copied to the clipboard using the standard 'Print screen' function ('Alt-PrtScn'). Using the command 'Plot Settings  $\rightarrow$  Notes & Annotations', you can also directly insert the cursor position in the plot as shown in fig. 2.3.

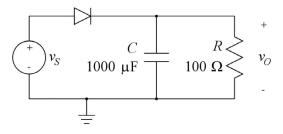

Next, we introduce a small change to the circuit: Instead of switching the voltage source  $v_S$  between 0 V and 5 V, we insert a switch as shown in fig. 2.4. The switch is open for t < 0, closes when t = 0 and re-opens at t = 2 ms. This will cause the capacitor to charge as before but the discharge will be only through  $R_2$ . In LTspice, the switch can be modeled by the component 'sw' from the component selection  $\mathcal{D}$ . This is a voltage controlled switch, so it requires a control voltage to specify the state of the switch. Unlike a resistor or a capacitor, the switch cannot be specified simply by a value. The properties of the switch are given in a '.model' specification in LTspice. You can find the detailed syntax for the required '.model' specification using the 'Help' function in LTspice.

**Figure 2.4:** The RC network from fig. 2.1 with a switch between the voltage source and the resistor  $R_1$ .

Figure 2.5: LTspice schematic and simulation results for the circuit in fig. 2.4.

When you insert the switch in the schematic, it appears with a reference to a default switch model SW. You may use the default model without inserting a '.model' specification. If you wish to change some parameters of the switch, you must include a '.model' specification and it is a good idea to use another name for the model, rather than the default SW.

Fig. 2.5 shows the LTspice schematic including a 'model' specification which is inserted using the command 'Edit  $\rightarrow$  SPICE Directive' (or the toolbar symbol 'p'). The 'model' specification first specifies that the device to be modeled is the device using the model name 'VSW' in the schematic. Next, the model used is the standard LTspice model 'SW' which is specified by some parameters given in the brackets. In this case, only the threshold of the switch is changed from the default value of 0 V, so that we can use the signal specification from fig. 2.2 for the control signal to the switch. Also note that the model is named VSW to distinguish it from the default name.

The '.model' specification is shown on the schematic with a smaller font size than otherwise used in the schematic. The font size is selected when inserting the specification (or when editing the specification). You can also make a 'global' change of the font size on schematics using the command 'Tools  $\rightarrow$  Control Panel' and the tab 'Drafting Options'.

In this schematic, the voltage  $V_S$  is specified as a dc voltage and the time varying signal to control the switch is the voltage source 'Vcontrol' which is specified as a piecewise linear voltage source with the same specification as the input voltage for the circuit in fig. 2.2. Also shown in fig. 2.5 is the simulation result for  $v_C$ , compare fig. 2.2.

It is clear from the simulation that the time constant for discharging the capacitor is now larger than the time constant for charging. The time constant for charging is the same as before, i.e. 240 µs. The time constant for discharging is now  $\tau = R_2 \times C = 600 \,\mu s$ . By scaling the voltage  $v_C$  in the same way as in fig. 2.3, you can use the cursors in the plot window to find the time constants. Note that two cursors are available, so by placing one cursor at the start time for the discharge (2 ms) and the other so that the vertical difference between the two cursors is 1 V, you can estimate the time constant to be the horizontal difference between the two cursors, see fig. 2.6.

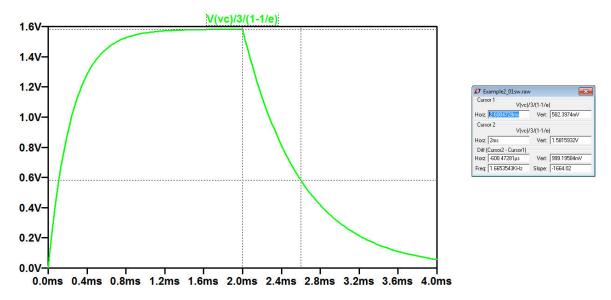

**AC response:** The circuit shown in fig. 2.1 is a first-order lowpass filter with the transfer function  $V_c(j\omega)/V_s(j\omega) = G_0/(1+j(\omega/\omega_0))$  where  $G_0 = R_2/(R_1+R_2) = 0.6$  (or -4.44 dB) is the low frequency gain and  $\omega_0 = 1/\tau = 1/((R_1 \parallel R_2) \times C)) = 4.17 \times 10^3 \text{ s}^{-1}$  (or 663 Hz) is the -3 dBfrequency. This frequency response is normally shown in a Bode plot. In LTspice, the transfer function is simulated using the '.ac' simulation command. Use 'Simulate → Edit Simulation Cmd' and select the tab 'AC Analysis'. Here you can specify the type of sweep, start frequency, stop

Get in-depth feedback & advice from experts in your topic area. Find out what you can do to improve the quality of your dissertation!

**Get Help Now**

Go to www.helpmyassignment.co.uk for more info

**Helpmy**assignment

Figure 2.6: Plot window with scaled output for finding the time constant.

frequency and number of points. For a Bode plot of the frequency response, it would be reasonable to select the type of sweep to be 'Octave' or 'Decade' starting at 10 Hz and ending at 100 kHz. The number of points per octave or decade may be selected to 10. When you click 'OK', the simulation command can be placed on the schematic. If you still have the transient simulation command in your schematic, it is changed into a comment.

Also the voltage source  $V_s$  must be specified. Right mouse click on the symbol and in the window with 'Advanced' settings set the AC amplitude for AC small signal analysis to 1. In this way, when plotting the output voltage  $V_c$ , the plot will directly show the transfer function. The DC bias point used for the '.ac' simulation is the bias point calculated with the value of  $V_s$  set to the initial value of the transient specification, in this example 0 V. If you need to specify a different DC bias value, you will have to set the time varying function to '(none)' in order to open the specification box for a DC value. Sometimes it can be advantageous to split the voltage source  $v_s$  into two separate, series connected voltage sources so that you do not have to remove the time varying specification but can set the desired bias value for the '.ac' simulation as the sum of the initial transient value and a series connected DC value.

Running the simulation opens a plot window with a horizontal frequency axis. When selecting  $V_c$  as the trace to show, both an amplitude plot and a phase plot appear as shown in fig. 2.7. In this plot, the colour of the curves has been changed from green to red to make the curves more visible and the vertical scales have been modified to the range 0 dB to -50 dB and  $0^{\circ}$  to  $-90^{\circ}$ .

Figure 2.7: LTspice schematic and AC simulation results for the lowpass filter from fig. 2.1.

The -3 dB frequency is found using the cursors in a way similar to what was done for finding time constants. You may either place one cursor at a very low frequency and move the second cursor until it is 3 dB below the first cursor and then read the position of the second cursor. Alternatively, just move a cursor to the frequency where the phase is  $-45^{\circ}$ . For a first order lowpass filter, this corresponds to the -3 dB frequency.

Be aware that the AC analysis is a small signal analysis calculated from the bias point of the circuit. For the circuit shown here with only linear components, the bias point is not important, but for circuits with non-linear components (e.g. MOS transistors), it is important to run the AC analysis from the correct bias point.

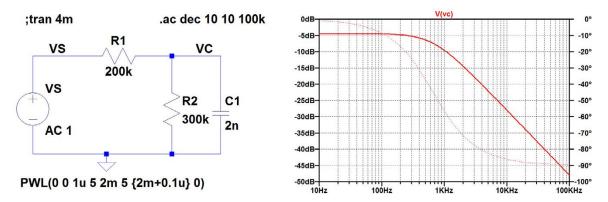

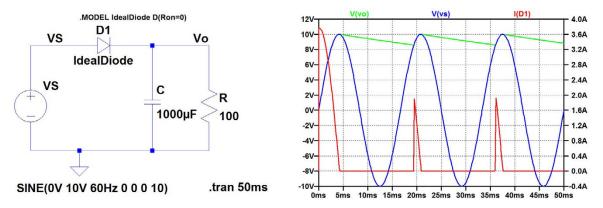

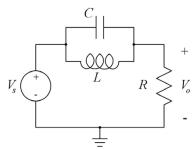

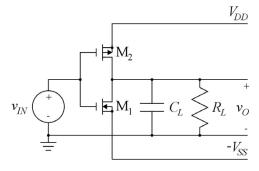

#### Example 2.2: A half-wave rectifier with a smoothing filter.

Figure 2.8: A half-wave rectifier with a smoothing filter.

The next example is a half-wave rectifier as shown in fig. 2.8. When drawing the schematic, the diode symbol is selected from the component selection box ( $\mathbf{D}$ ). Like the switch in fig. 2.5, the diode is modeled by a '.model' specification. If you omit the '.model' specification, the diode defaults to the standard Shockley model  $i_D = I_S[\exp(v_D/(nV_T)) - 1]$  (Hambley 2014) where the default value of the saturation current is  $I_S = 10^{-14}$  A and the default value of the emission coefficient is n = 1.  $V_T$  is the thermal voltage (26 mV at room temperature).

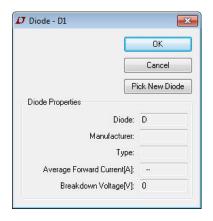

Several models for different commercially available discrete type diodes are included with LTspice and are contained in a library file. When selecting the diode, you point to the centre of the diode symbol. This turns the cursor into a hand . A right mouse click opens a window as shown in fig. 2.9. By clicking 'Pick New Diode', you open a window with a selection of standard component diodes. Selecting a diode and clicking 'OK' will insert the diode name on the schematic and insert a link to the appropriate '.model' statement in the LTspice netlist file. If the selected diode is a Zener diode (or another type of diode), the symbol is also changed into the appropriate diode symbol.

Figure 2.9: Window for selecting diode model.

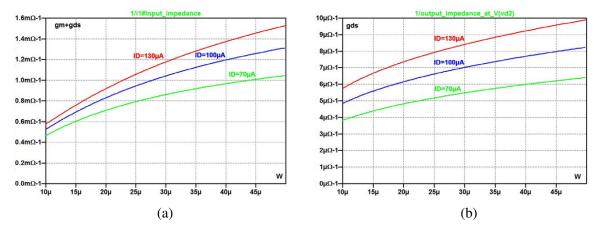

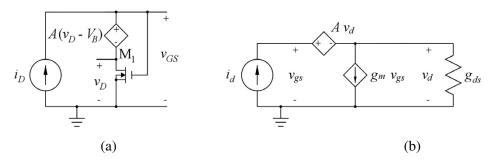

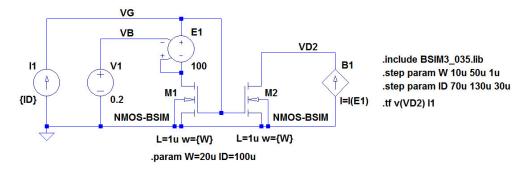

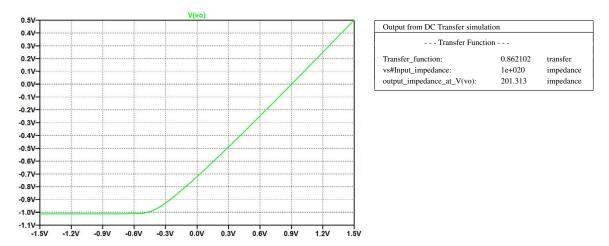

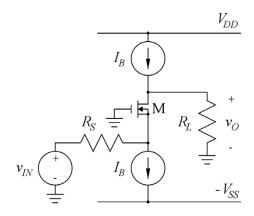

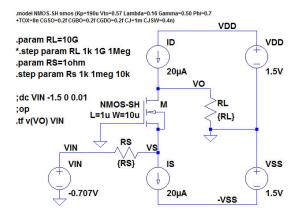

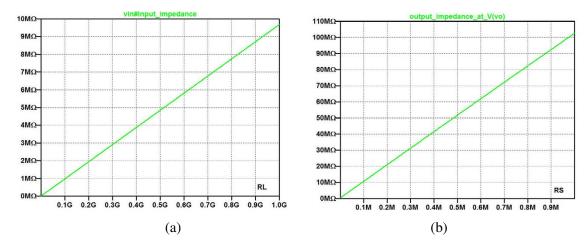

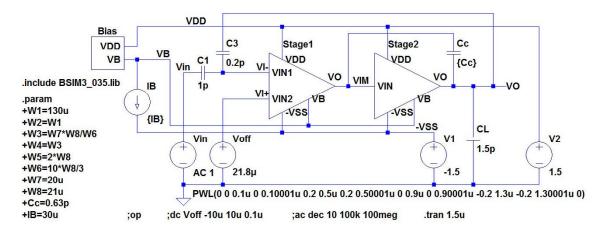

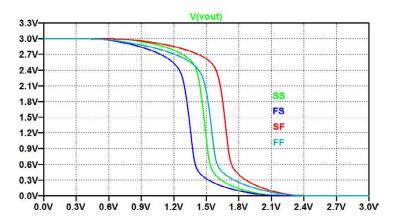

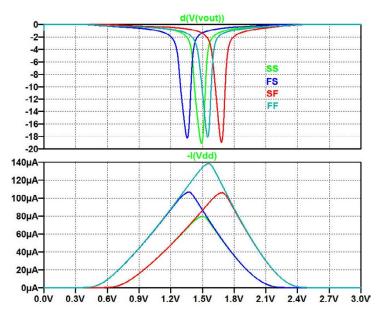

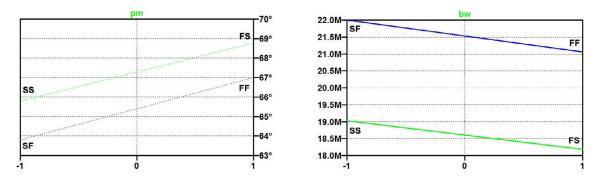

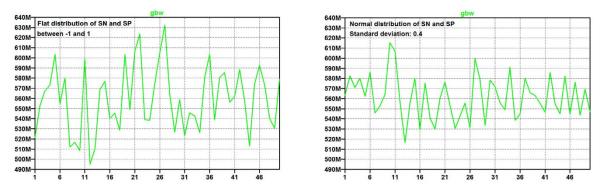

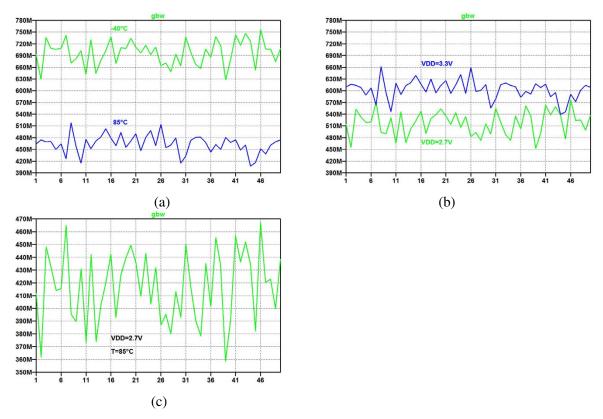

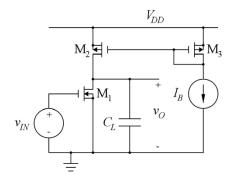

Alternatively, you can specify your own diode model. You can find a description of the parameters for the diode model using LTspice 'Help'. In addition to the Shockley diode model, LTspice provides the option of using a piecewise linear diode model in which you can specify the resistance in forward direction and in reverse direction and a forward threshold voltage to enter conduction. You may also specify the reverse breakdown region (particularly useful for a Zener-diode), see the 'Help' function in LTspice where you can also find the default values of the parameters. If you specify just one of the parameters for the piecewise linear model, this model will be used rather than the Shockley model.